GAN MICROWAVE DC-DC CONVERTERS

by

IGNACIO RAMOS FRANCO B.S., University of Illinois at Chicago, 2009 M.S., University of Colorado, 2013

A thesis submitted to the Faculty of the Graduate School of the University of Colorado in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical and Computer Engineering

August 2016

This thesis entitled:

#### GaN Microwave DC-DC Converters

#### written by Ignacio Ramos Franco

has been approved for the Department of Electrical and Computer Engineering

Zoza Parta Zoya Popović

bragan chak nuović Dragan Maksimović

Date July 6, 2016

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards

of scholarly work in the above mentioned discipline.

Ramos Franco, Ignacio (Ph.D., Electrical Engineering)

GaN Microwave DC-DC Converters

Thesis directed by Professor Zoya Popović

Increasing the operating frequency of switching converters can have a direct impact in the miniaturization and integration of power converters. The size of energy-storage passive components and the difficulty to integrate them with the rest of the circuitry is a major challenge in the development of a fully integrated power supply on a chip. The work presented in this thesis attempts to address some of the difficulties encountered in the design of high-frequency converters by applying concepts and techniques usually used in the design of high-efficiency power amplifiers and high-efficiency rectifiers at microwave frequencies. The main focus is in the analysis, design, and characterization of dc-dc converters operating at microwave frequencies in the low gigahertz range.

The concept of PA-rectifier duality, where a high-efficiency power amplifier operates as a high-efficiency rectifier is investigated through non-linear simulations and experimentally validated. Additionally, the concept of a self-synchronous rectifier, where a transistor rectifier operates synchronously without the need of a RF source or driver is demonstrated. A theoretical analysis of a class-E self-synchronous rectifier is presented and validated through non-linear simulations and experiments.

Two GaN class- $E^2$  dc-dc converters operating at a switching frequency of 1 and 1.2 GHz are demonstrated. The converters achieve 80% and 75% dc-dc efficiency respectively and are among the highest-frequency and highest-efficiency reported in the literature. The application of the concepts established in the analysis of a self-synchronous rectifier to a power amplifier culminated in the development of an oscillating, selfsynchronous class- $E^2$  dc-dc converter.

Finally, a proof-of-concept fully integrated GaN MMIC class- $E^2$  dc-dc converter switching at 4.6 GHz is demonstrated for the first time to the best of our knowledge. The 3.8 mm × 2.6 mm chip contains distributed inductors and does not require any external components. The maximum measured dc-dc efficiency is approximately 45 %.

## DEDICATION

A mis padres, por haberme inculcado la importancia y el valor de la educación ...

and to coffee and beer for helping me get here.

### Personal Acknowledgments

It has been a great pleasure to experience graduate school with everyone in the CU microwave group. I would like to especially thank Andrew Zai, Sean "Honey badger" Korhummel, Scott Schaffer, Rob Scheeler, Mike Litchfield, and Mike Coffey for keeping the atmosphere in the lab fun and interesting and making grad school a very enjoyable experience. I'll always cherish DOTA breaks and the darts nights at downers.

I am very grateful to have worked with current and past members in the CU microwave group including Michael Roberg, Erez Falkenstein, Frank Trang, Jon Chisum, Dan Kuester, Xavier Palomer, David Sardin, Cesar Sanchez, Asmitha Dani, Jennifer Imperial, Mauricio Pinto, Gregor Lasser, Sushia Rahimizadeh, Parisa Momenroodaki, Patrick Blum, Jose Antonio Estrada, Allison Duh, William Haines, Jerome Cherome, Leonardo Ranzzani, and Maxwell Duffy.

Finally I would like to thank my parents, my brother Eloy, and my sister Maricela for all their support throughout the years.

### **PROFESSIONAL ACKNOWLEDGMENTS**

First I would like to thank my adviser Prof. Zoya Popović for funding me and giving me the opportunity to attend graduate school. I am thankful for all the knowledge and professional advice she has bestowed on me. I would also like to thank Prof. Dragan Maksimović for all the time and guidance he provided me with through my studies at CU Boulder. Dr. Tibault Reveyrand deserves special recognition for helping me with anything related to non-linear modeling and for serving as a measurements guru. I would also like to thank Prof. Jose Angel García from the University of Cantabria for all the useful comments, edits, and for being an excellent collaborator.

I'm also very thankful to the rest of the members of my PhD committee and all the other professor from the University of Colorado who have taught me so much including Prof. Edward Kuester, Prof. Dejan Filipović, and Prof. Khurram Afridi. Additionally, my undergrad adviser Prof. Danillo Erricolo from the University of Illinois at Chicago deserves credit for encouraging me to attend graduate school.

I would like to thank ARPA-E for funding most of the research presented in this thesis under the ADEPT program and ARPA-E IDEAS. Additionally, I extend my gratitude to QORVO, especially Dr. Charles Campbell for all his help and advise to the entire CU microwave group.

# Contents

| L | IST O | of Tables                                                                      | xi  |

|---|-------|--------------------------------------------------------------------------------|-----|

| L | IST O | of Figures                                                                     | xii |

| 1 | Int   | RODUCTION                                                                      | 1   |

|   | 1.1   | Thesis outline and chapter overview                                            | 4   |

| 2 | Bac   | ckground for High Frequency DC-DC Converters                                   | 7   |

|   | 2.1   | DC-DC CONVERTERS AT HIGH FREQUENCIES AND SWITCHING LOSSES                      | 8   |

|   |       | 2.1.1 High-frequency switching losses and soft switching                       | 9   |

|   | 2.2   | Magnetics                                                                      | 12  |

|   |       | 2.2.1 Winding losses                                                           | 13  |

|   | 2.3   | Semiconductor device technology                                                | 15  |

|   | 2.4   | Summary and conclusion                                                         | 18  |

| 3 | Pov   | wer Amplifier (PA)-Rectifier Duality                                           | 19  |

|   | 3.1   | Introduction                                                                   | 20  |

|   | 3.2   | Time reversal duality and the class- $E^2$ converter                           | 21  |

|   |       | 3.2.1 Synthesis of a class- $E^2$ DC-DC Converter                              | 21  |

|   |       | 3.2.1 Analysis of a class-E rectifier                                          | 23  |

|   | 3.3   | Non-linear simulations of microwave power amplifiers, microwave rectifiers and |     |

|   |       | THEIR DUALITY                                                                  | 29  |

|   |       | 3.3.1 Simulation of the power amplifier                                        | 29  |

|   | 3.4 | Exper  | imental validation of PA-rectifier duality with a $\mbox{class-}F^{-1}$ power amplifier $% f(x)=0$ . | 33 |

|---|-----|--------|------------------------------------------------------------------------------------------------------|----|

|   |     | 3.4.1  | Circuit design                                                                                       | 33 |

|   |     | 3.4.2  | Measurement setup                                                                                    | 34 |

|   |     | 3.4.3  | Self-synchronous transistor rectifier results                                                        | 35 |

|   | 3.5 | Self-s | YNCHRONOUS RECTIFIER                                                                                 | 40 |

|   |     | 3.5.1  | Theoretical analysis of self-synchronous rectifier                                                   | 40 |

|   |     | 3.5.2  | Non-linear model simulations                                                                         | 44 |

|   |     | 3.5.3  | Experimental validation                                                                              | 49 |

|   | 3.6 | Concl  | USION                                                                                                | 51 |

| 4 | RF  | CLAS   | s-E <sup>2</sup>                                                                                     |    |

|   | DC  | -DC C  | Converter Design                                                                                     | 53 |

|   | 4.1 | Introi | DUCTION                                                                                              | 54 |

|   | 4.2 | Synch  | ironous class- $E^2$ DC-DC converter                                                                 | 56 |

|   |     | 4.2.1  | Design and fabrication                                                                               | 56 |

|   |     | 4.2.2  | Measurement results for the synchronous converter $\ldots \ldots \ldots \ldots$                      | 59 |

|   | 4.3 | CLASS  | - $E^2$ DC-DC converter with self-synchronous rectifier                                              | 62 |

|   |     | 4.3.1  | Design and fabrication                                                                               | 62 |

|   |     | 4.3.2  | Measurement results for the converter with self-synchronous rectifier $\ . \ .$                      | 63 |

|   |     | 4.3.3  | Estimate of losses in the converter                                                                  | 64 |

|   | 4.4 | Oscili | Lating, self-synchronous class $E^2$ DC-DC converter $\ldots \ldots \ldots \ldots$                   | 67 |

|   |     | 4.4.1  | Design and fabrication                                                                               | 68 |

|   |     | 4.4.2  | Measurement results for oscillating, self-synchronous converter $\ldots$ .                           | 70 |

|   |     | 4.4.3  | Estimate of losses in the converter                                                                  | 72 |

|   | 4.5 | Concl  | JUSION                                                                                               | 74 |

| 5 | Dis   | TRIBUTED CLASS- $E^2$ DC-DC Converter           |     |

|---|-------|-------------------------------------------------|-----|

|   | Mie   | crowave Monolithic Integrated                   |     |

|   | Cir   | CUIT (MMIC)                                     | 76  |

|   | 5.1   | Introduction                                    | 76  |

|   | 5.2   | Design of integrated converter                  | 78  |

|   | 5.3   | Measurements with synchronous rectifier         | 85  |

|   | 5.4   | Measurements with self-synchronous operation    | 87  |

|   | 5.5   | Losses estimate and efficiency improvement      | 89  |

|   | 5.6   | Conclusion                                      | 91  |

| 6 | Ne    | ar-field Capacitive Wireless Power              |     |

|   | Tra   | ansfer Array For Electric Vehicles              | 93  |

|   | 6.1   | Introduction                                    | 93  |

|   | 6.2   | Design and description of capacitive WPT system | 95  |

|   | 6.3   | Full wave electromagnetic model                 | 99  |

|   | 6.4   | Conclusion                                      | 105 |

| 7 | Sui   | MMARY AND FUTURE WORK                           | 106 |

|   | 7.1   | Summary                                         | 106 |

|   | 7.2   | Contributions                                   | 107 |

|   | 7.3   | Future Work                                     | 110 |

| B | IBLIC | DGRAPHY 1                                       | 14  |

| A | PPEN  | IDICES                                          |     |

| A | Lov   | w Power Wireless Energy Harvester               | 129 |

|   | A.1   | Introduction                                    | 129 |

|   | A.2   | Design and integration of rectifier and antenna | 131 |

|   | A.3 | Measurements and Results                                   | 33         |

|---|-----|------------------------------------------------------------|------------|

|   |     | A.3.1 Alternate Design with the Skyworks SMS7630-079 Diode | 33         |

|   | A.4 | Conclusion                                                 | 35         |

| В | Mic | CRO-COAXIAL DECADE-BANDWIDTH                               |            |

|   | DC- | ISOLATED TRANSFORMERS 13                                   | 36         |

|   | B.1 | INTRODUCTION                                               | 36         |

|   | B.2 | Device design                                              | 37         |

|   | B.3 | RF and DC measurements                                     | 39         |

|   | B.4 | Discussion and conclusion                                  | <b>1</b> 2 |

# LIST OF TABLES

| 2.1 | Soft-switched vs. hard-switched loss                                 | 11 |

|-----|----------------------------------------------------------------------|----|

| 2.2 | Typical RF inductors from coilcraft                                  | 15 |

| 2.3 | Table of properties of major wide band-gap materials                 | 16 |

|     |                                                                      |    |

| 3.1 | Summary of electrical quantities and their time-reversal equivalents | 21 |

| 3.2 | Summary of X-band amplifier measured as a PA and as a rectifier      | 49 |

|     |                                                                      |    |

| 4.1 | High frequency DC-DC converters comparison                           | 55 |

| 4.2 | Summary of estimated losses                                          | 67 |

| 4.3 | Estimated losses based on simulation                                 | 74 |

# LIST OF FIGURES

| 1.1 | Photograph of a traditional 10-W dc-dc converter module from Texas Instruments. The            |    |

|-----|------------------------------------------------------------------------------------------------|----|

|     | model is the PTMA403033                                                                        | 2  |

| 1.2 | High-level block diagram of a resonant dc-dc converter                                         | 3  |

| 1.3 | Progression of the design of the GHz dc-dc converter compared to a commercial example.         |    |

|     | The goal of the thesis is to first design a watt level hybrid dc-dc converter operating around |    |

|     | 1 GHz with a low profile on a PCB using GaN on SiC Microwave transistors. After realizing      |    |

|     | a 1 GHz converter, complete monolithic integration is pursued to achieve a monolithically      |    |

|     | integrated dc-dc converter, with the GaN chip ( $2.3 \times 3.8$ mm) shown on the right        | 4  |

| 2.1 | Voltage and current waveforms comparison between a hard-switch transition (a) and the          |    |

|     | soft-switching transition of a class-E amplifier (b). The voltage and current waveforms are    |    |

|     | normalized to the voltage and current of the supply.                                           | 10 |

| 2.2 | Simplified model of a MOSFET and the main parasitic components that cause power loss.          |    |

|     | The simplified model ignores the coupling drain to gate capacitance $C_{gd}$                   | 11 |

| 2.3 | Top view of (a) fabricated magnetic-core microinductor and (b) air-core inductor compared      |    |

|     | in [1]                                                                                         | 13 |

| 2.4 | Simplified GaN HEMT structure and main parasitic components                                    | 17 |

| 3.1 | Diagram of the synthesis of dc-dc converters by cascading fundamental two-port networks .      | 22 |

| 3.2 | Schematic of ideal Class-E power amplifier                                                     | 22 |

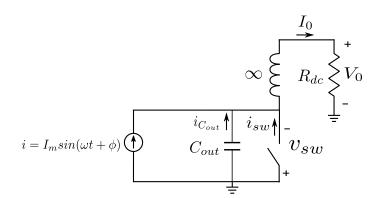

| 3.3 | Class-E rectifier circuit                                                                      | 23 |

| 3.4 | Simplified model of a Class-E rectifier.                                                       | 23 |

| 3.5  | Simplified model of a Class-E rectifier when the switch is closed                                                                                                         | 25 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

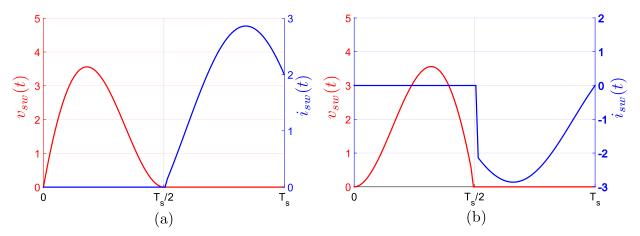

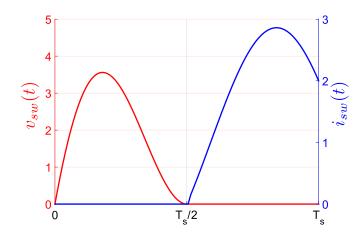

| 3.6  | Voltage and current time-domain waveforms across the switching element of a class-E PA                                                                                    |    |

|      | (a) and a class-E rectifier. The waveforms are normalized to the dc voltage and current of                                                                                |    |

|      | the supply or load. The waveforms are time-reversal dual of each other.                                                                                                   | 27 |

| 3.7  | Schematic of ideal Class-E rectifier.                                                                                                                                     | 28 |

| 3.8  | Schematic of a class- $E^2$ dc-dc converter composed of a class-E PA and its time-reversal dual                                                                           |    |

|      | class-E rectifier.                                                                                                                                                        | 28 |

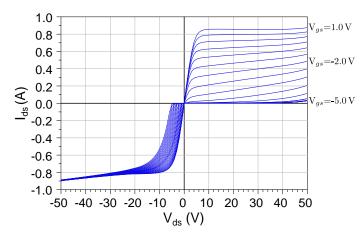

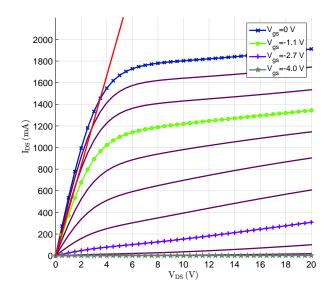

| 3.9  | I-V curves of the 8 x 75 $\mu$ m GaN HEMT model used in all the non-linear simulations                                                                                    | 30 |

| 3.10 | Schematic of the semi-ideal power amplifier simulation. The input and output matching                                                                                     |    |

|      | networks are implemented using ideal impedance tuners. The impedance of the fundamental                                                                                   |    |

|      | frequency as well as the first 5 harmonics are terminated by the tuner                                                                                                    | 30 |

| 3.11 | Load-pull simulations for rectifier efficiency obtained at transistor terminals. Frequency is                                                                             |    |

|      | 2.14 GHz and RF drain input power is 40 dBm. Marker shows impedance for maximum                                                                                           |    |

|      | efficiency                                                                                                                                                                | 31 |

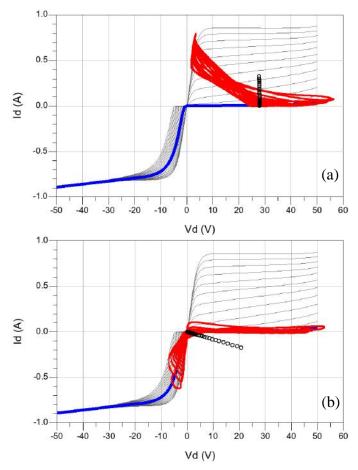

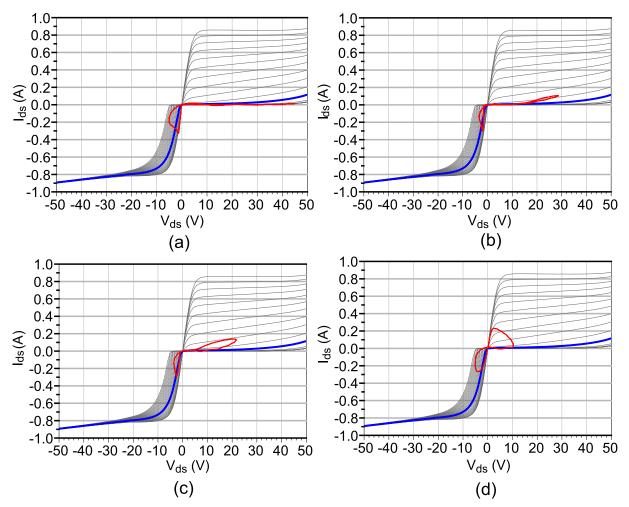

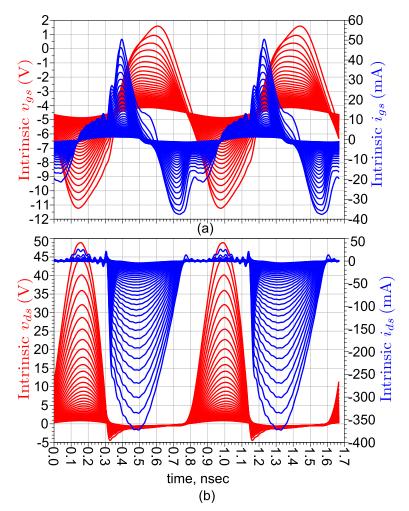

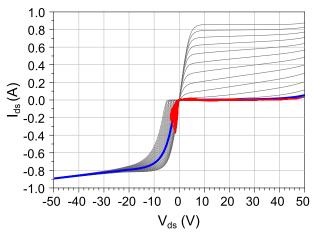

| 3.12 | Simulated GaN transistor I-V curves (grey), dynamic load lines (red) and drain DC voltage                                                                                 |    |

|      | and current (black) for PA (a) and rectifier (b). Blue line corresponds to the I-V curves of                                                                              |    |

|      | $V_{gs} = -4.9$ V, the quiescent bias voltage of the rectifier. Time-reversal duality is seen as RF                                                                       |    |

|      | power at drain is swept from 0 to 40 dBm at 2.14 GHz                                                                                                                      | 32 |

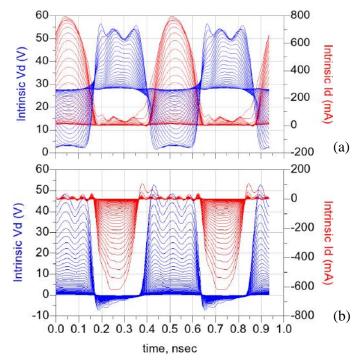

| 3.13 | Simulated time-domain intrinsic drain voltage (blue) and current (red) waveforms for RF                                                                                   |    |

|      | input power ranging from 0 to 40 dBm at intrinsic drain of power amplifier (a) and rectifier (b).                                                                         | 33 |

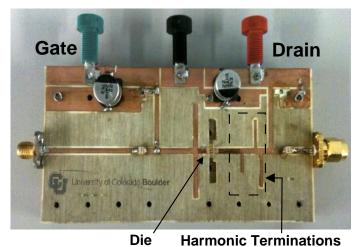

| 3.14 | Photograph of the class- $F^{-1}$ power amplifier, working at 2.14 GHz and presented in [2]                                                                               | 34 |

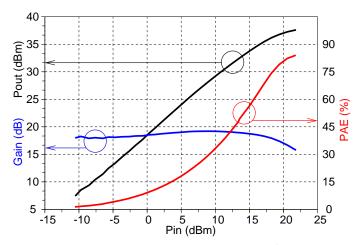

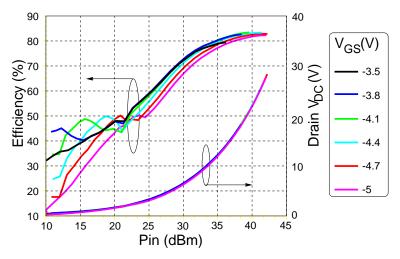

| 3.15 | Large-signal measurements performed on the class- $F^{-1}$ power amplifier at $f_0 = 2.14$ GHz,                                                                           |    |

|      | $V_{GS} = -3.8 \text{ V} \text{ and } V_{DS} = 28 \text{ V} \dots $ | 34 |

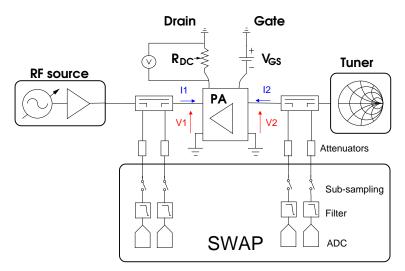

| 3.16 | Time-domain non-linear rectifier measurement block diagram. The SWAP [3] performs                                                                                         |    |

|      | sampling of current and voltage and the calibration refers the sampled quantities to the                                                                                  |    |

|      | reference planes at the DUT. The drain output DC resistance $R_{DC}$ , the gate bias $V_{GS}$ and the                                                                     |    |

|      | gate RF impedance $Z_g$ are varied as the input power at the drain is swept from 10 to 42 dBm.                                                                            | 36 |

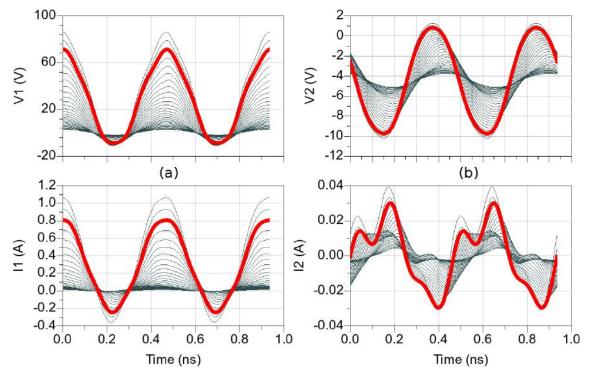

| 3.17 Time-domain waveforms measured at drain (a) and gate (b) of the rectifier with $V_{GS} = -4.4$ V,             |

|--------------------------------------------------------------------------------------------------------------------|

| $R_{DC} = 98.5 \Omega$ and $Z_g(f_0) = (230 + j10) \Omega$ . The RF input power at the drain is swept from         |

| 10 to 42 dBm, corresponding to the range of output power of the class- $F^{-1}$ PA                                 |

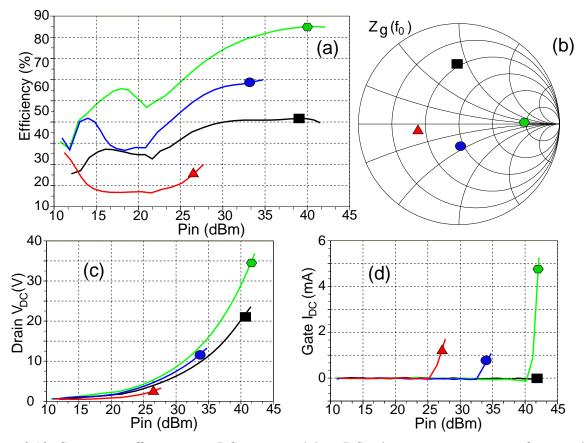

| 3.18 Conversion efficiency, gate DC current and drain DC voltage versus input power for several RF                 |

| load impedance values presented at the gate. $V_{GS} = -4.4$ V and $R_{DC} = 98.5 \Omega$ . The green              |

| point on the Smith chart corresponds to the highest efficiency point at $Z_g(f_0) = (230 + j10) \Omega$ . 38       |

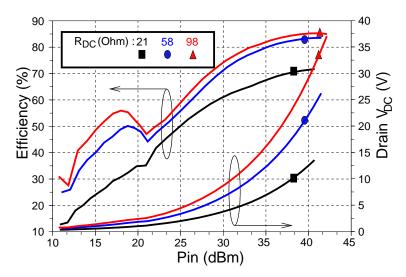

| 3.19 Conversion efficiency and drain DC output voltage versus input power for several DC drain                     |

| resistor values. $V_{GS} = -4.4V$ and $Z_g(f_0) = (230 + j.10) \Omega$ . The highest efficiency of 85%             |

| is obtained at $P_{in}$ =40 dBm with a $V_{DC}$ =30 V                                                              |

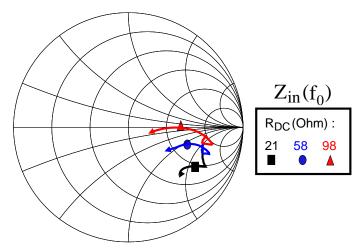

| 3.20 RF impedance at $f_0$ measured at the input (drain port) versus input power for several DC                    |

| drain resistor values. $V_{GS} = -4.4V$ and $Z_g(f_0) = (230 + j10) \Omega$                                        |

| 3.21 Measured conversion efficiency and drain DC voltage versus input power for several DC gate                    |

| voltage biases. For this data, $R_{DC} = 58\Omega$ and $Z_g(f_0) = (230 + j10)\Omega$                              |

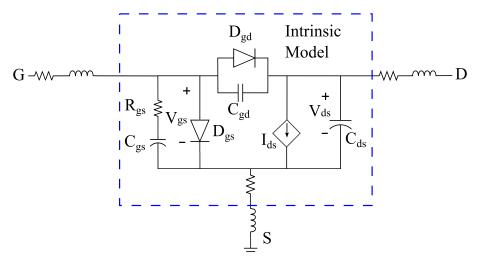

| 3.22 Simplified intrinsic model of a GaN HEMT. Diodes $D_{gd}$ and $D_{gs}$ are modeled as open                    |

| circuits for self-synchronous analysis                                                                             |

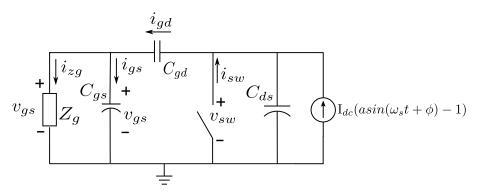

| 3.23 Idealized switch model for class-E self-synchronous conditions. The switch is assumed                         |

| ideal, with $R_{on}=0$ and $R_{off}=\infty$ . $v_{sw}$ is assumed to be an ideal class-E waveform, and $v_{gs}$ is |

| approximated as a sinusoid. Unknown impedance $Z_g$ is found under these conditions 41                             |

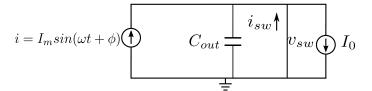

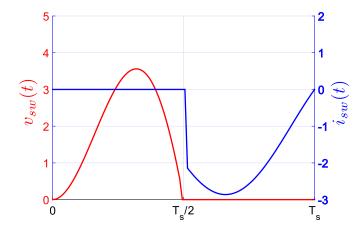

| 3.24 Time domain waveforms of an ideal class-E rectifier. The waveforms are normalized. $v_{sw}$ is                |

| assumed across the switch in Fig. 3.23                                                                             |

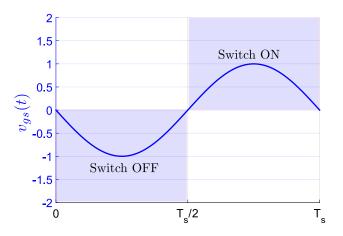

| 3.25 Operation of the switch as a function of assumed $v_{gs}$ . The switch is off for $v_{gs} \le 0$ , and on     |

| for $v_{gs} > 0$                                                                                                   |

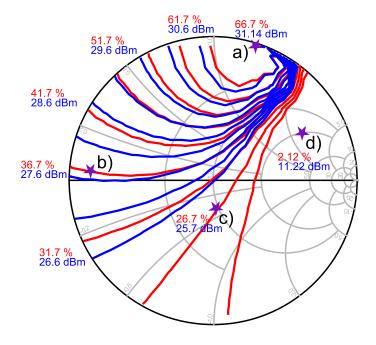

| 3.26 RF-DC efficiency contours (Red) and DC output power contours (blue) obtained in a load                        |

| pull simulation preformed at the gate port of a class-E self-synchronous rectifier using an                        |

| improved non-linear GaN HEMT model [4,5]. Results are obtained under a $V_{gs}$ =-4 V bias,                        |

| $R_{DC}$ = 90 $\Omega$ and an input power of 33 dBm (2 W). Impedance points a, b, c, and d, correspond             |

| to the impedance at the gate port for the dynamic load lines presented in Fig. 3.27 45                             |

| 3.27 | Simulated dynamic load line (red) corresponding to impedance points a, b, c, and d in             |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | Fig. 3.26. The blue line shows the I-V curves for the quiescent bias ( $V_g = -4$ V)              | 46 |

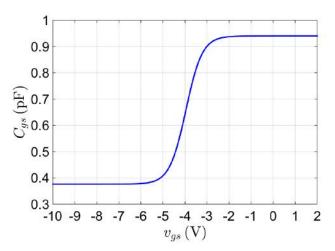

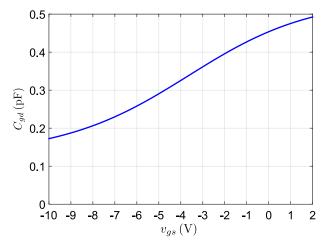

| 3.28 | Simulated non-linear capacitance $C_{gs}$ as a function of $v_{gs}$ for the 8x75 $\mu$ m GaN HEMT |    |

|      | model [4,5]                                                                                       | 47 |

| 3.29 | Simulated non-linear capacitance $C_{gd}$ as a function of $v_{gs}$ for the 8×75 $\mu$ m GaN HEMT |    |

|      | model [4,5]                                                                                       | 47 |

| 3.30 | Time domain waveforms of class-E rectifier. Voltage and current waveforms at intrinsic gate       |    |

|      | (a), and at intinsic drain (b). Waveforms are shown for input powers varying from 0-35 dBm        |    |

|      | in dB steps.                                                                                      | 48 |

| 3.31 | Simulated dynamic load line (red), and I-V curves of quiescent bias (blue) for class-E self-      |    |

|      | synchronous rectifier for an input power range of 0-35 dBm with $Z_g$ resonating equivalent       |    |

|      | input capacitance at 1.22 GHz. As expected, transistor minimizes power dissipation and            |    |

|      | approximates an ideal diode.                                                                      | 49 |

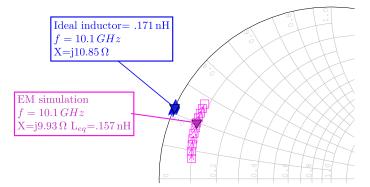

| 3.32 | Comparison between the impedance presented to the gate of the transistor when the rectifier       |    |

|      | is operated self-synchronously (Pink) and the ideal 0.171 nH inductor (blue) required to          |    |

|      | resonate the 1.45 pF input capacitance of the transistor. The figure shows the impedance          |    |

|      | presented to the transistor resonates the input capacitance above the operating frequency of      |    |

|      | 10.1 GHz                                                                                          | 50 |

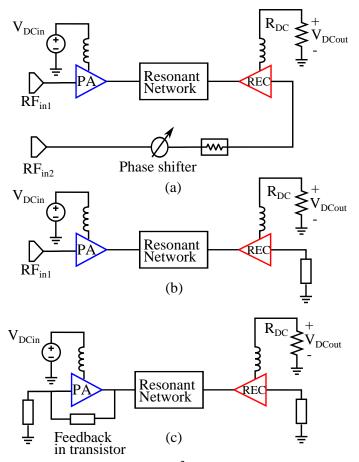

| 4.1  | Block diagram of high frequency class- $E^2$ dc-dc converter. (a) a synchronous topology; (b)     |    |

|      | a self-synchronous topology with a single RF input at the inverter input; and (c) a oscillating,  |    |

|      | self-synchronous topology with no RF inputs.                                                      | 56 |

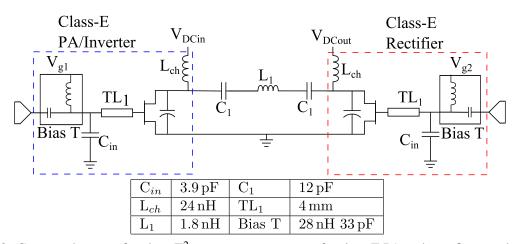

| 4.2  | Circuit schematic for class- $E^2$ converter consisting of a class-E PA and rectifier coupled     |    |

|      | through a resonant network. The value of all components is given in the table                     | 58 |

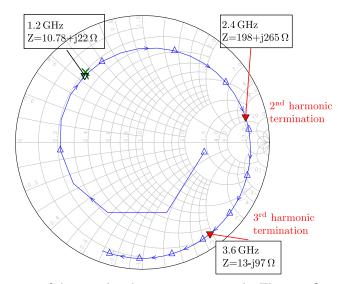

| 4.3  | Frequency response of the simulated inter-stage network. The rectifier transistor is replaced                         |    |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

|      | by the ideal resistive load given by $\operatorname{Re}\{Z_{net}\}$ and high frequency models from Modelithics        |    |

|      | are used for all the passive components. The termination of the second and third harmonics                            |    |

|      | are shown at 2.4 and 3.6 GHz. The green marker indicates the targeted impedance at the                                |    |

|      | fundamental.                                                                                                          | 59 |

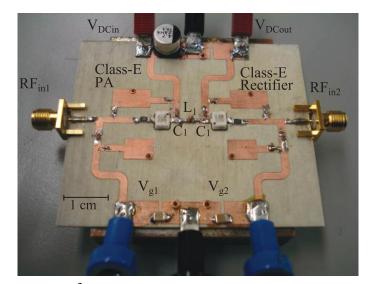

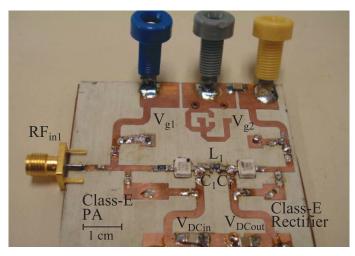

| 4.4  | Photograph of class- $E^2$ converter prototype. The left side of the circuit is the class-E                           |    |

|      | inverter and the right a synchronous rectifier. They are coupled through the reactive network                         |    |

|      | consisting of $L_1$ =1.8 nH and $C_1$ = 12 pF                                                                         | 60 |

| 4.5  | Setup used to characterize the class- $E^2$ converter prototype. The output voltage is enforced                       |    |

|      | by the electronic load while the current is allowed to be set by the converter itself                                 | 60 |

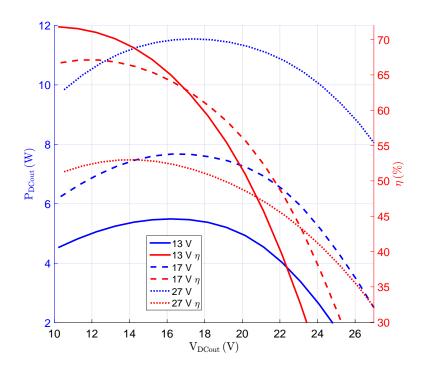

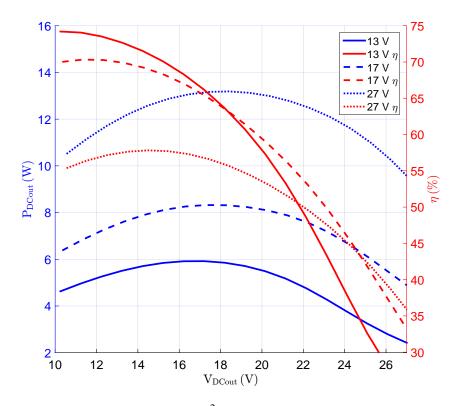

| 4.6  | Measured converter efficiency (red) and output power (blue) plotted as a function of output                           |    |

|      | voltage for input voltages of 13, 17 and 27 V                                                                         | 61 |

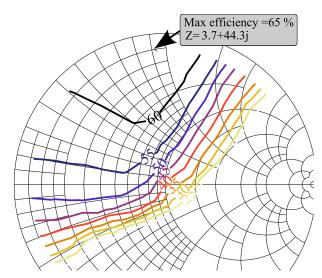

| 4.7  | Impedance constellation and efficiency contours produced by a load pull performed at the                              |    |

|      | gate port of the rectifier for maximum efficiency for a DC output voltage of 17 V. The Smith                          |    |

|      | chart is normalized to $50 \Omega$                                                                                    | 62 |

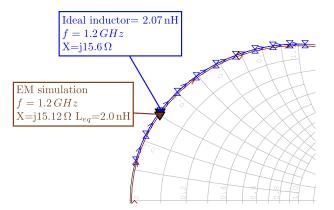

| 4.8  | Comparison between the impedance presented by the rectifier's input matching network EM                               |    |

|      | simulated (Brown) and the ideal 2.07 nH inductor (blue) required to resonate the 8.5 pF input                         |    |

|      | capacitance of the T2G001528 transistor model. The figure shows the impedance of the                                  |    |

|      | matching network closely follows the impedance of the ideal inductor around the switching                             |    |

|      | frequency.                                                                                                            | 63 |

| 4.9  | Photograph of class- $E^2$ converter with the rectifier operating self-synchronously. The RF                          |    |

|      | port at the gate of the rectifier is removed and the input matching network is modified to                            |    |

|      | present the optimum impedance to the rectifier. The size of the circuit board is $5.6 \text{ cm}$ by $6 \text{ cm}$ . | 63 |

| 4.10 | Measured self-synchronous class- $E^2$ converter efficiency (red) and output power (blue) as a                        |    |

|      | function of output voltage for input voltages of 13, 17 and 27 V                                                      | 64 |

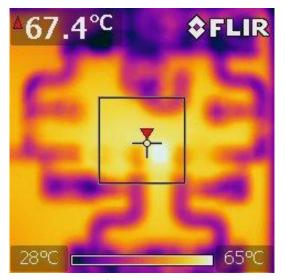

| 4.11 | Infrared photograph of the class- $E^2$ dc-dc converter after operating for a full day. Emissivity         |    |

|------|------------------------------------------------------------------------------------------------------------|----|

|      | is not calibrated therefore the photograph is only meant to serve as a comparison between                  |    |

|      | components                                                                                                 | 67 |

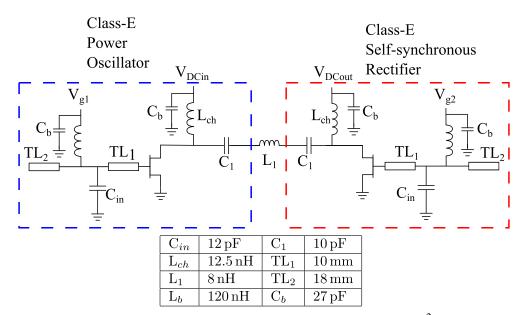

| 4.12 | Circuit schematic for self-oscillating, self-synchronous class- $E^2$ DC-DC converter                      | 69 |

| 4.13 | Time domain waveforms of an ideal class-E amplifier and oscillator. The waveforms are                      |    |

|      | normalized                                                                                                 | 69 |

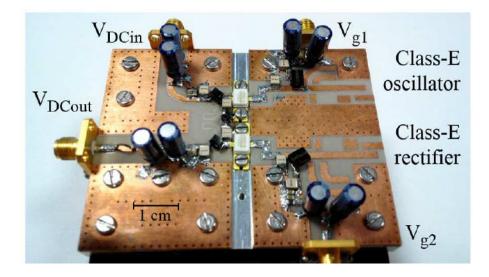

| 4.14 | Photograph of oscillating, self-synchronous class- $E^2$ DC-DC converter                                   | 71 |

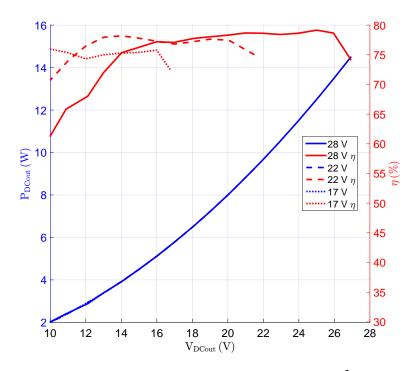

| 4.15 | Measured performance of oscillating, self-synchronous class- $E^2$ DC-DC converter. Con-                   |    |

|      | verter efficiency (red) and output power (blue) plotted as a function of output voltage for                |    |

|      | input voltages of 17, 22 and 28 V                                                                          | 72 |

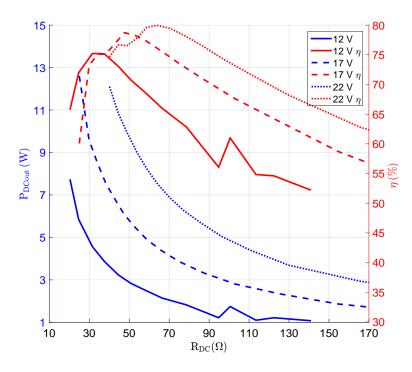

| 4.16 | Measured performance of $V_{out}$ control through $V_{g1}$ for oscillating, self-synchronous con-          |    |

|      | verter. Input voltage is 28 V while output voltage is adjusted to 12, 17 and 22 V                          | 73 |

| 5.1  | Simulated I-V curves for the $12 \times 100 \mu$ m transistor device used in the design of the distributed |    |

|      | converter. The red line is used to estimate $R_{ON}$ when the transistor is fully ON                       | 79 |

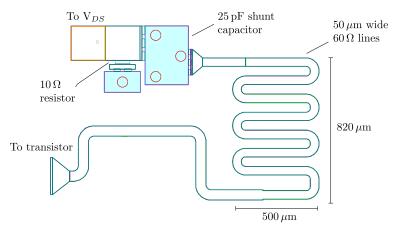

| 5.2  | Layout of the output bias-T. Because the distributed nature of the circuit, the bias-T does not            |    |

|      | appear like an open circuit at the fundamental frequency and it becomes a matching element.                | 80 |

| 5.3  | Frequency response of EM simulated Bias-T from DC to 30 GHz. The bias-T does not look                      |    |

|      | like an open circuit at $f_0$ and becomes part of the output matching network                              | 81 |

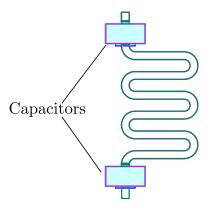

| 5.4  | Layout of CLC resonator used between the two transistors of a distributed class- $E^2$ converter.          |    |

|      | The two capacitors are 5.7 pF, given process variation                                                     | 81 |

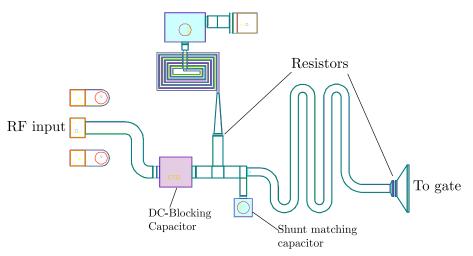

| 5.5  | Layout of the input matching network.                                                                      | 82 |

| 5.6  | Setup used to optimize the design of the converter. The rectifier's switch is replaced by the              |    |

|      | equivalent resistor the class-E rectifier presents to the class-E inverter under ideal operation.          |    |

|      | The simulation is used to optimize the design for maximum DC-RF efficiency                                 | 82 |

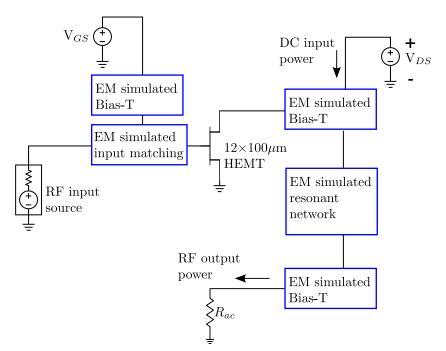

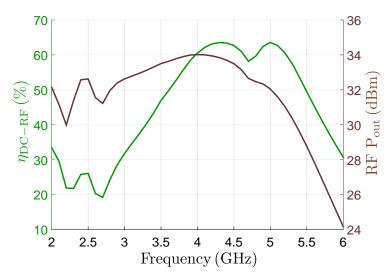

| 5.7  | DC-RF efficiency and RF output power as a function of frequency after performing an                        |    |

|      | optimization of the circuit shown in Fig. 5.6.                                                             | 83 |

| 5.8  | Frequency response of the EM simulated output-matching network after optimizing the entire       |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | design for maximum PA efficiency.                                                                | 84 |

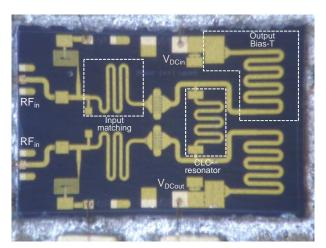

| 5.9  | Photograph of the monolithically integrated class- $E^2$ DC-DC converter. The total area of the  |    |

|      | die is 2.5 mm × 3.8 mm                                                                           | 84 |

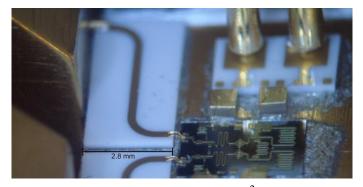

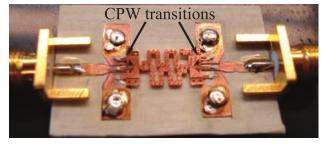

| 5.10 | Photograph of the fixture used to measure the class- $E^2$ MMIC. The two RF inputs are           |    |

|      | connected to the alumina lines via two bondwires. The center pin of the launchers is settled     |    |

|      | on the alumina line. The gate and drain DC pads are connected to a 1000 pF capacitor shunt       |    |

|      | to ground and then connected to DC pads for external pins (two cylinder on top) to make          |    |

|      | contact with.                                                                                    | 85 |

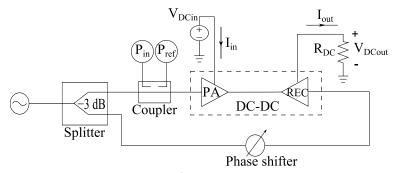

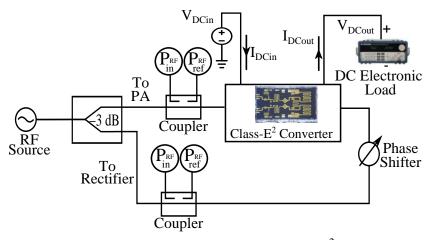

| 5.11 | Setup used to characterize the monolithic integrated class- $E^2$ converter. The RF source is    |    |

|      | split in two signals, one is driving the PA and the other one drives the rectifier. The incident |    |

|      | and reflected power of the driving signal is measured using two couplers. The phase of           |    |

|      | the signal driving the rectifier is adjusted for synchronous operation. The output voltage is    |    |

|      | enforced by the electronic load                                                                  | 86 |

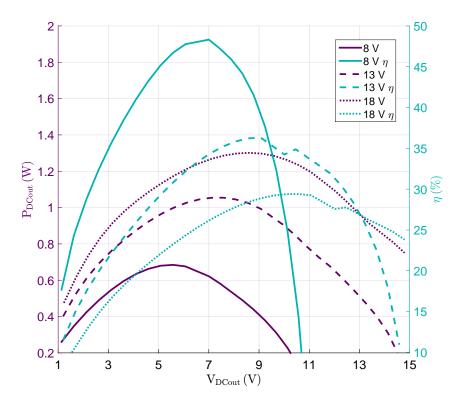

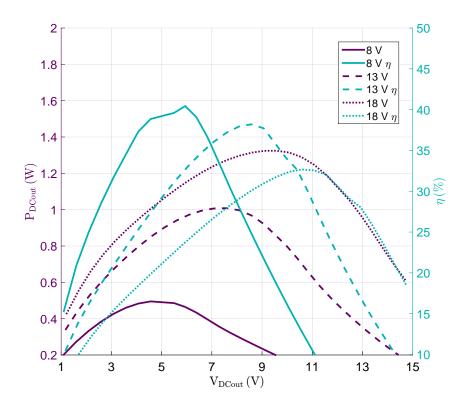

| 5.12 | Measured results of the integrated converter. Efficiency (cyan) is shown in the right y-axis     |    |

|      | and output power (purple) is shown in the left y-axis; both are plotted at 4.5 GHz as a function |    |

|      | of output voltage for an input voltage of 8, 13 and 18 V                                         | 87 |

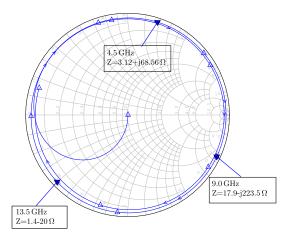

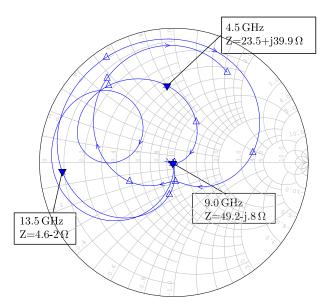

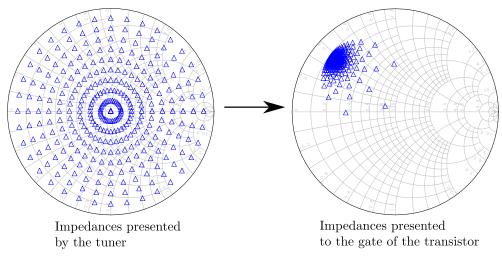

| 5.13 | Simulation of the transformation of the impedances presented by an ideal tuner to the            |    |

|      | impedances presented to the gate of the transistor after the launchers, alumina-lines, wire      |    |

|      | bonds, and input matching network of the MMIC. The results are shown at 4.5 GHz                  | 88 |

| 5.14 | Measured output power and efficiency of the integrated converter with the rectifier running      |    |

|      | self-synchronously. Efficiency (cyan) is shown in the right y-axis and output power (purple)     |    |

|      | is shown in the left y-axis; both are plotted as a function of output voltage for input voltages |    |

|      | of 8, 13 and 18 V                                                                                | 89 |

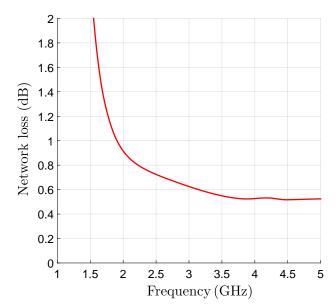

| 5.15 | EM simulated loss in the network of the distributed converter.                                   | 90 |

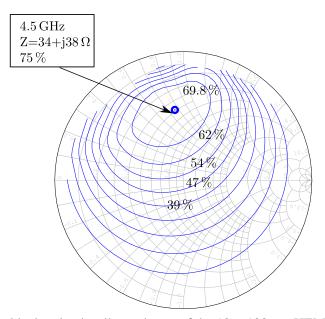

| 5.16 | Results of ideal losless load-pull simulation of the $12 \times 100 \mu\text{m}$ HEMT used in the design.       |

|------|-----------------------------------------------------------------------------------------------------------------|

|      | The simulation is performed at 4.5 GHz with the $2^{nd}$ and $3^{rd}$ harmonic optimized for                    |

|      | efficiency. The maximum efficiency obtained is 75 %                                                             |

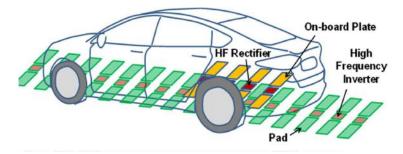

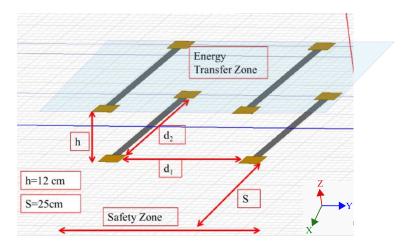

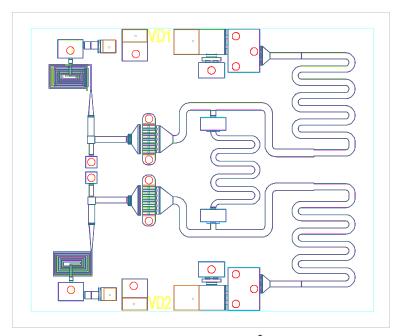

| 6.1  | Diagram of the proposed capacitive wireless power system                                                        |

| 6.2  | Reference levels for general public exposure to time-varying electric and magnetic fields                       |

|      | according to ICNIRP [6]                                                                                         |

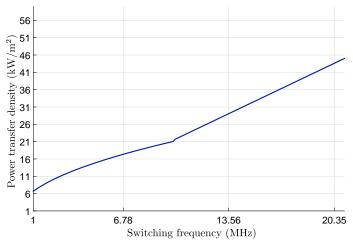

| 6.3  | Maximum achievable power transfer density for a single module with $2.5 \text{ cm} \times 5 \text{ cm}$ plates, |

|      | a current gain G <sub>2</sub> =10, a full bridge rectifier (Krec= $8/\pi^2$ ), a gap between the plates d=12 cm |

|      | and the maximum E-field according to Fig. 6.2 measured 25 cm from the plates 97                                 |

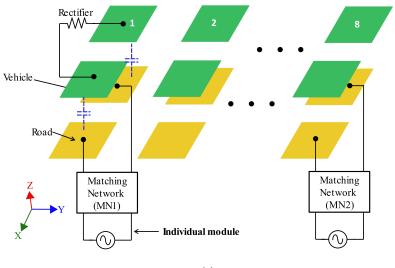

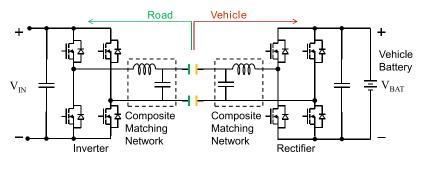

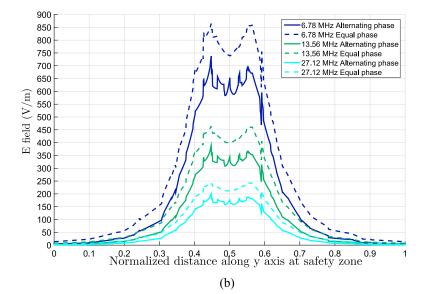

| 6.4  | (a) Block diagram of the capacitive array wireless power transfer system for a stationary                       |

|      | vehicle. $N$ pairs of plates are placed in the road, with inverters (dc-ac converters) connected                |

|      | between each pair. $N$ identical pairs of plates are placed on the bottom of the vehicle, with                  |

|      | rectifiers connected between the plates, closing the current loop with the plates in the ground.                |

|      | (b) Equivalent circuit of an individual WPT module, consisting of 4 plates, a resonant inverter                 |

|      | and a rectifier                                                                                                 |

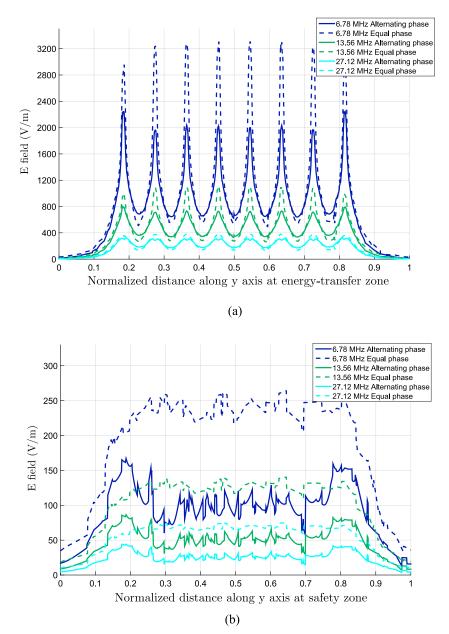

| 6.5  | Depiction of zones where the magnitude of the electric field is calculated                                      |

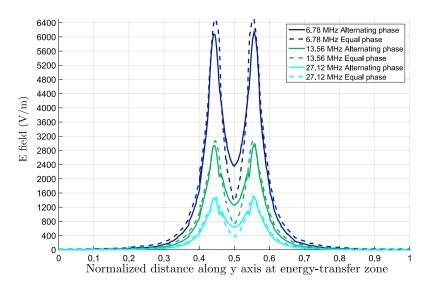

| 6.6  | Magnitude of the electric field calculated at the plane of the safety zone for a two-module                     |

|      | system at three ISM-band frequencies under consideration. Dashed lines show the E-field                         |

|      | with inverter modules in phase, while the solid line shows the E-field with modules having                      |

|      | alternating 180° phases                                                                                         |

| 6.7  | Magnitude of the electric field calculated at the plane of the safety zone for a five-module                    |

|      | system at three ISM-band frequencies under consideration. Dashed lines show the E-field                         |

|      | with inverter modules in phase, while the solid line shows the E-field with modules having                      |

|      | alternating 180° phases                                                                                         |

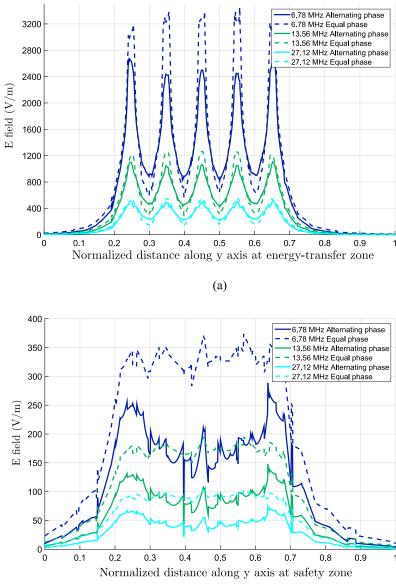

| 6.8 | Magnitude of the electric field calculated at the plane of the safety zone for a eight-module                |

|-----|--------------------------------------------------------------------------------------------------------------|

|     | system at three ISM-band frequencies under consideration. Dashed lines show the E-field                      |

|     | with inverter modules in phase, while the solid line shows the E-field with modules having                   |

|     | alternating 180° phases                                                                                      |

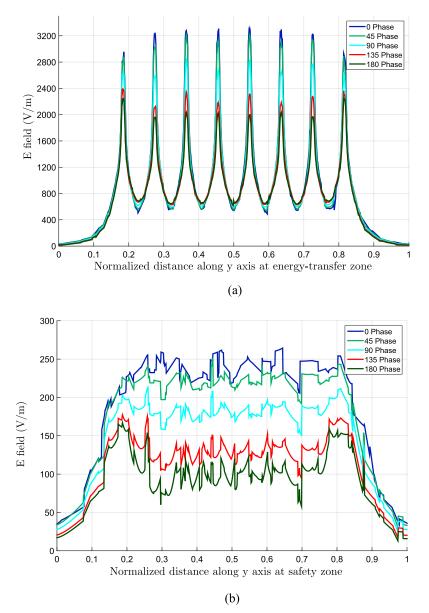

| 6.9 | Magnitude of electric field as a function of normalized distance along the body of the car at                |

|     | 6.78 MHz in the energy-transfer zone (a) and safety zone (b) for different alternating phases                |

|     | between modules                                                                                              |

| 7.1 | Proposed layout for a version of the integrated $E^2$ dc-dc converter with the gate impedance                |

|     | terminated on-chip. The converter operates without the need of a high-frequency source 112                   |

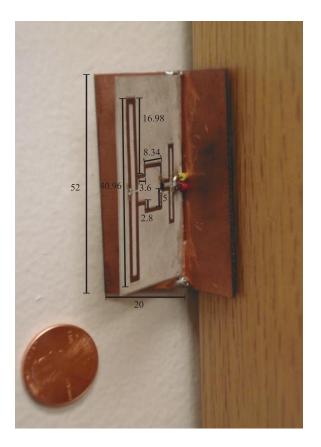

| A.1 | Photograph of energy harvester prototype with a Skyworks SMS7630-079. All dimensions                         |

|     | are given in millimeters                                                                                     |

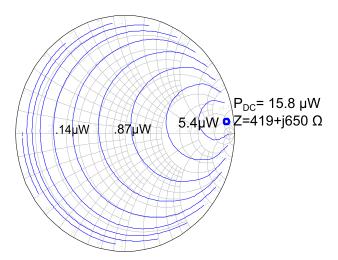

| A.2 | Simulated load pull contours for the W-band ZBD diode from VDI, performed with an                            |

|     | incident power of -15 dBm and a DC load of $2.2 \text{ k}\Omega$ . Maximum rectified power achieved          |

|     | is 15.8 $\mu W$ at an impedance of 419+650 $\Omega$ . The contours represent constant DC rectified           |

|     | power in $\mu$ W                                                                                             |

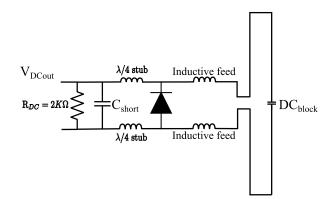

| A.3 | Simplified schematic of rectenna circuit. $C_{short} = 10 \text{ pF}$ , a DC blocking capacitor $DC_{block}$ |

|     | is placed at the symmetry plane of the dipole to behave as a short circuit at 2.45 GHz and                   |

|     | avoid short circuiting the diode                                                                             |

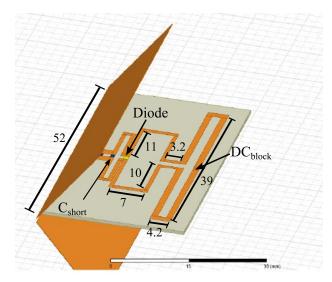

| A.4 | Layout of the rectenna with the VDI diode match, corresponding to the circuit diagram in                     |

|     | the previous figure. The DC load is connected on the back of the reflector though vias. All                  |

|     | dimensions are given in mm                                                                                   |

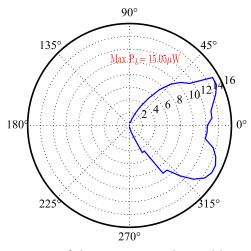

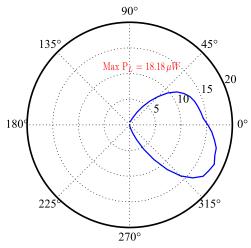

| A.5 | Measured radiation pattern of the rectenna is obtained by measuring the DC power across the                  |

|     | load and includes the efficiency change over angle. The incident power density is $1 \mu\text{W/cm}^2$       |

|     | and the DC load is 2.2 kΩ. The rectified power is shown in $\mu$ W, with a peak of 15.05 $\mu$ W 134         |

| A.6 | Pattern of rectified power as a function of azimuth angle for Skyworks SMS7630-079 diode.                        |

|-----|------------------------------------------------------------------------------------------------------------------|

|     | Measurements are performed with a 1 $\mu$ W/cm <sup>2</sup> incident power density and a 2.2 k $\Omega$ DC load. |

|     | Rectified power is shown in $\mu$ W. The maximum rectifed power is 18.05 $\mu$ W                                 |

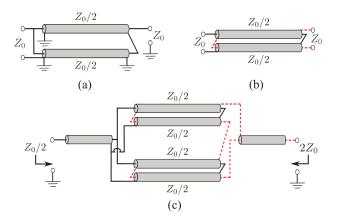

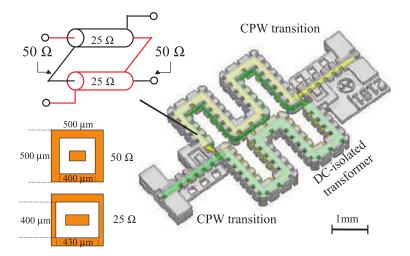

- B.1 Circuit schematics of (a) a traditional Guanella, (b) a 1:1 and (c) 4:1 dc-isolated transformers.In the dc-isolated transformers the colors and line types (red dashed/black continuous)identify the separate dc paths.

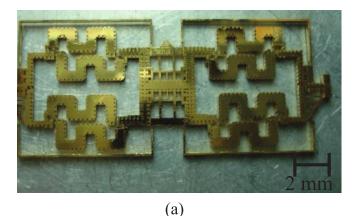

- B.3 Layout of the fabricated 1:1 transformer. Two rectangular microcoaxial lines are interconnected as shown in Fig. B.1(b). The coaxial lines have  $500 \,\mu\text{m} \times 500 \,\mu\text{m}$  cross section. The inner conductor cross section is  $200 \,\mu\text{m} \times 155 \,\mu\text{m}$  for the  $50 \,\Omega$  lines and  $200 \,\mu\text{m} \times 220 \,\mu\text{m}$ for the internal  $25 \,\Omega$  lines.

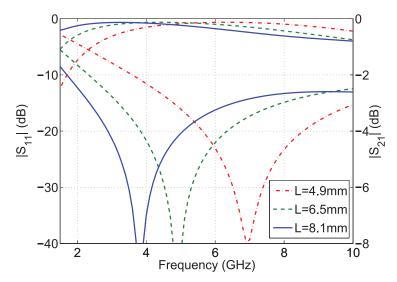

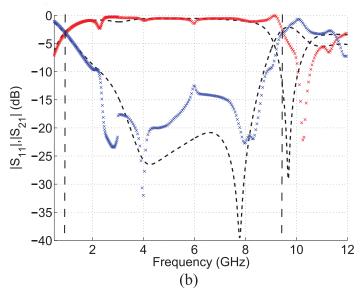

- B.5 (a) Photograph of the isolated microfabricated transformer with microcoaxial to CPW transition. A 1 mm wide cut in the center of the microstrip ground plane, so that the input and output microstrip grounds are connected inside the Vector Network Analyzer used for testing. (b) Transmission and return loss. Full-wave simulations are plotted in a dashed line. 141

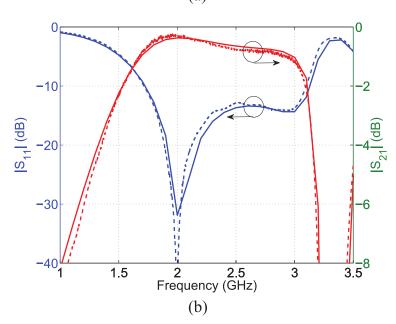

- B.6 (a) Photograph of the fabricated back-to-back 50:25:50 Ω transformer prototype. (b) Measured transmission and return loss. Full-wave electromagnetic simulations are plotted in dashed lines.

### Chapter 1

### INTRODUCTION

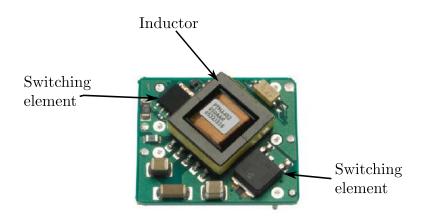

The research presented in this thesis addresses fundamental concepts involved in designing dc-dc converter circuits that operate at frequencies that are three orders of magnitude higher than current high-speed converters in commercial power supplies. The miniaturization and integration of the power supply and voltage regulators in a system can achieve significant improvements in the overall miniaturization and manufacturability of electronics. Traditional switching power supplies are very efficient, reliable, robust, and are well understood. However, the manufacturing focuses on the assembly of modules or bricks from discrete components, instead of focusing on integrated hardware solutions derived from semiconductor and microelectronics technologies [7]. A traditional 10-W dc-dc converter module from TI is shown in Fig. 1.1. It can be observed that discrete passive components take a significant portion of real estate in the converter module. In specific, magnetic components such as inductors and transformers, have been proven difficult to effectively integrate with the rest of the converter.

The size and value of energy-storage components such as capacitors, inductors, and transformers, is inversely proportional to frequency. Fundamentally, increasing the switching frequency of power converters should reduce the size of converters to be as compact as possible. There are, however, practical constraints that severely limit the switching frequency of converters. The leading cause being a severe decrease in efficiency by a number of factors exacerbated at higher frequencies.

Figure 1.1: Photograph of a traditional 10-W dc-dc converter module from Texas Instruments. The model is the PTMA403033

Increasing the switching frequency of of dc-dc converters with a goal of reduced size, faster transient response, and increased power density was attempted early in the development of switching converters [8–10]. Nonetheless, recently there has been a renewed interest in increasing the operating frequency of converters [11–14] encouraged by the availability of wide-bandgap semiconductors and higher performance, fast transistors. For instance, part of this thesis was funded by the Agile Delivery of Electrical Power Technologies (ADEPT) program from the Advanced Research Project Agency-Energy (ARPA-E). The ADEPT program funded several teams to develop and demonstrate the effectiveness of SiC and GaN devices in power converters. Moreover, in 2013 ARPA-E launched the SWITCHES (Strategies for Wide Bandgap, Inexpensive Transistors for Controlling High-Efficiency Systems) program, which focuses on the development of high voltage (1200 V) high current (100 A) single die power semiconductor devices using SiC, GaN, and diamond [15].

Lately, the European Union program for research and technological development FP7 funded the project "'Power Supply With Integrated PassivEs" or PowerSwipe. The PowerSwipe consortium proposed to develop the next generation Power Supply in Package (PwrSip) and Power Supply on Chip (PWrSoC) technology platforms by investigating innovations in integrated power passives, nanoCMOS technologies, and advanced packaging [16]. The inability to integrate the power passive components for high efficiency dc-dc converters was determined to be a major roadblock in the integration of low efficiency linear regulators, switched capacitors converters, and switched-mode dc-dc converters with the micro-controller SoC. A review of high frequency, highly integrated inductive dc-dc converters is shown in [17], where all but one of the converters are implemented in Si-CMOS and are therefore limited to low voltage, and low power.

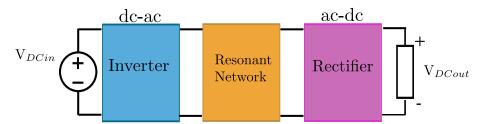

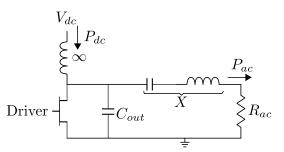

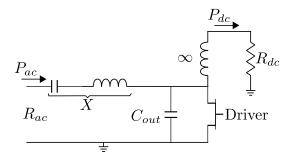

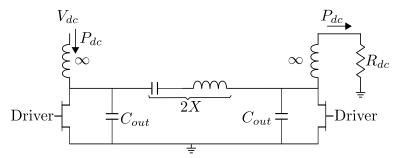

The work presented in this thesis attempts to address some of the difficulties encountered in the design of high-frequency converters by applying concepts more commonly used in the design of high-efficiency power amplifiers and rectifiers at microwave frequencies. Fundamentally, a resonant dc-dc converter is composed of three main blocks as shown in Fig. 1.2: a dc-ac converter implemented as an inverter, an amplifier or an oscillator; a resonant coupling network that can be realized with inductors and capacitors; and an ac-dc converter implemented by a diode or transistor rectifier circuit. High-efficiency in PAs and rectifiers at microwave frequencies is obtained by wave-shaping through harmonic terminations that enable low power dissipation at the switching element. Load pull is an essential tool that facilitates determination of matching impedances that enable design of wave-shaping networks [18–20] and can applied to the resonant converter from Fig. 1.2.

Figure 1.2: High-level block diagram of a resonant dc-dc converter

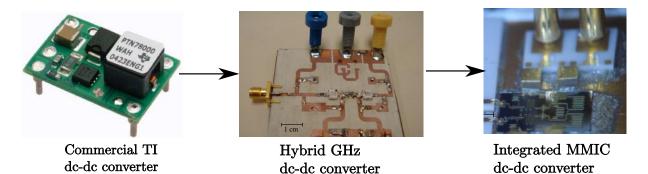

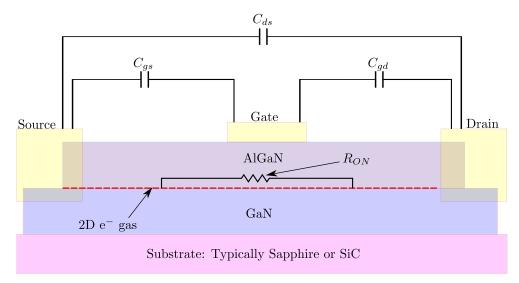

The main goal of the thesis is illustrated in Fig. 1.3. The first part of the thesis investigates different configurations of the fundamental resonant converter shown in Fig. 1.2 to first realize a hybrid dc-dc converter operating in the 1-GHz region which is implemented on a printed circuit board with low-profile components. The substantial increase in switching frequency is pursued to later explore the possibility of a monolithically integrated dc-dc converter using processes normally used in monolithic microwave integrated circuits (MMICs) where the implementation is with transmission lines. Because of the high switching frequencies, GaN on SiC high electron mobility transistors (HEMTs) are used in all the designs instead of the more typical metal-oxide-semiconductor field-effect transistor (MOSFETs).

Figure 1.3: Progression of the design of the GHz dc-dc converter compared to a commercial example. The goal of the thesis is to first design a watt level hybrid dc-dc converter operating around 1 GHz with a low profile on a PCB using GaN on SiC Microwave transistors. After realizing a 1 GHz converter, complete monolithic integration is pursued to achieve a monolithically integrated dc-dc converter, with the GaN chip  $(2.3 \times 3.8 \text{ mm})$  shown on the right.

#### 1.1 Thesis outline and chapter overview

The organization of this thesis and a summary of each chapter are presented below.

Chapter 2 presents an overview of important concepts and some of the challenges encountered in the design of high-frequency converters. The discussion provides a basic understanding of the main problems encountered in the design of dc-dc converters at high frequencies, as relevant to this thesis. Switching losses associates with FET transistors are first overviewed, followed by a review of high-frequency losses in magnetic components commonly used in dc-dc converters. The advantages of wide-bandgap semiconductor devices, such as gallium nitride HEMS are discussed along with a comparison with typical Silicon power MOSFETs.

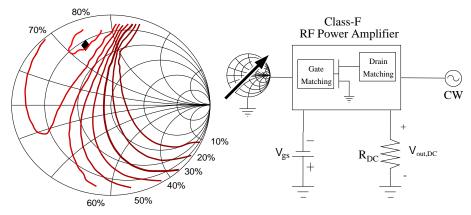

Chapter 3, details the concept of time-reversal duality for PAs and rectifiers proposed originally by David C. Hamill in 1990, and applies the concept to microwave dc-dc converters. Analysis of a class-E rectifier and the design of a class- $E^2$  dc-dc converter is also shown together with non-linear simulations of a GaN transistor operating as a PA and as its time-reversal dual rectifier. Further, experimental validation of the time-reversal results are given on the example of a 2.14 GHz class- $F^{-1}$  PA as a power amplifier and as a rectifier. Finally, an idealized theoretical analysis of a class-E self-synchronous rectifier is given. The proposed analysis is validated using nonlinear harmonic-balance simulations and measurements.

Chapter 4 presents the design and experimental demonstration of class- $E^2$  dc-dc converters operating around 1 GHz. The design methodology relies on PA-rectifier duality and the design of a high-efficiency class- $E^2$  converter consisting of a high-efficiency class-E RF power amplifier and a high-efficiency class-E power rectifier presented in Chapter 3. Synchronous, self-synchronous, and oscillating, self-synchronous converters are demonstrated with hybrid circuits using GaN on SiC packaged HEMTs. The oscillating, self-synchronous converter is part of a collaboration with Prof. Jose Angel Garciá from the University of Cantabria in Santander, Spain. The efficiency of this 1-GHz converter reaches nearly 80 % with over 10 W of output dc power.

Chapter 5 demonstrates the feasibility of a resonant converter consisting of only distributed passive components. A completely distributed class- $E^2$  dc-dc converter is designed in Qorvo's 0.15  $\mu$ m GaN on SiC process as a proof-of-concept demonstration of a fully monolithically integrated dc-dc converter. A detailed description of the MMIC design is given. The distributed converter is then measured with the rectifier driven synchronously and a manual external tuner is used to operate the rectifier self-synchronously. Finally, losses in the converter and efficiency improvements are addressed.

The microwave dc-dc converters from chapter 3-5 all contain a PA(inverter) reactively coupled to a rectifier. This coupling is implemented with capacitors and inductors, but can also be accomplished using impedance transformers (such as the ones presented in appendix B), or through electric and magnetic fields more generally.

In Chapter 6, the concepts from previous chapters are applied to wireless power transfer (WPT), where the coupling between the PA and the rectifier from Fig. 1.2 is accomplished through electric and magnetic near-fields. Near-field wireless power transfer has been most commonly done using inductive coupling at lower frequencies (100 kHz-13 MHz). The applications range from sub-watt implants to electric vehicles and industrial machinery. In this chapter, an array approach to capacitive WPT aimed at a modular and scalable system for charging electric vehicles is presented. The goal of the distributed array approach is to increase maximum transferable power while decreasing the fringing electric field produced by the WPT system, accomplished by field focusing through phase control. In this kW-level WPT system, the full-bridge inverter and rectifier are designed by Prof. Kurram Afridi and the power electronics group at the University

of Colorado at Boulder, while the goal of the work presented in this thesis is to determine the focusing effects at different frequencies and for several array configurations and relative phasing between the modules is shown. The primary frequencies of interest are the 6.78, 13.56 and 27.12 MHz ISM bands.

Specific contributions of the thesis are discussed in the concluding chapter, a long with some directions for future work. Most of the content of this thesis has been published in [21-26].

### Chapter 2

# BACKGROUND FOR HIGH FREQUENCY DC-DC Converters

#### **CONTENTS**

| 2.1 | DC-DC CONVERTERS AT HIGH FREQUENCIES AND SWITCHING LOSSES |   |  |  |

|-----|-----------------------------------------------------------|---|--|--|

|     | 2.1.1 High-frequency switching losses and soft switching  | 9 |  |  |

| 2.2 | Magnetics                                                 | 2 |  |  |

|     | 2.2.1 Winding losses                                      | 3 |  |  |

| 2.3 | Semiconductor device technology                           | 5 |  |  |

| 2.4 | Summary and conclusion                                    | 8 |  |  |

This chapter presents an overview of important concepts and some of the challenges encountered in the design of high-frequency converters. The discussion provided in this chapter is not intended to serve as a comprehensive review of high-frequency dc-dc converters or power electronics, it only aims to provide a basic understanding of the main problems encountered in the design of high-frequency converters that are relevant to this thesis. For a more comprehensive analysis of power electronics, the reader is referred to "Fundamentals of Power Electronics" by Erickson and Maksimović [27].

The chapter is divided as follows: Section 2.1 overviews switching losses associates with FET transistors in high-frequency converters. In Section 2.2, high-frequency magnetic components commonly used in dc-dc converters are reviewed briefly. Section 2.3 shows a brief overview of the advantages wide bandgap semiconductor devices such as gallium nitride devices have over typical Silicon power MOSFETs.

#### 2.1 DC-DC CONVERTERS AT HIGH FREQUENCIES AND SWITCHING LOSSES

Increasing the switching frequency of dc-dc converters to just the VHF range between 3-300 MHz brings with it a plethora of opportunities as well as challenges [11]. [12] presents a summary of the evolution of very high frequency (VHF) power supplies. The merger of circuit techniques used in radio frequency power amplifiers and those used in classical power electronics starts to develop at VHF frequencies. Power amplifiers are generally divided in classes characterized by the amount of time the power transistor conducts. A class-A power amplifier conducts 100 % of the time and has a maximum theoretical efficiency of 50 % . A class-B PA conducts 50 % of the time and has a maximum theoretical efficiency of 78.5 %. A class-C PA conducts between 0-25 % of the time and has a theoretical maximum efficiency of 100 %. These amplifier classes are the power electronics equivalent of linear regulators; detailed analysis of their operation is shown in [19, 28, 29] and will not be repeated here.

A class-D PA, first invented by Baxandall in 1959 [30] is considered a switching power amplifier because the power transistor is operated as a switch. The class-D PA has a maximum theoretical efficiency of 100 % and does not suffer from high voltage levels at the power transistor. The power electronics equivalent to the class-D amplifier are typically the half-bridge and full-bridge converters. Detailed analysis of class-D amplifiers is shown in [29].

Class-F and class- $F^{-1}$  PAs introduced by Tyler in 1919 [31] utilize harmonic resonators to shape the voltage and current across the switching element in order to minimize current and voltage overlap and consequentially minimize power dissipation in the transistor. Class-F PAs can achieve very high efficiencies and have been widely used to improve efficiency of RF transmitters. The power electronics equivalent topologies are multi-resonant converters that use zero-voltage (ZVS) or zero-current (ZCS) switching techniques. When

a circuit operates in ZVS, the transistor turns ON when there is zero voltage across the transistor, and when it operates in ZCS, the transistor turns OFF at zero current. A more detail explanation of ZVS is shown below. Similarly, the class-E PA first introduced by Sokal in 1975 [32], displaces the current and voltage waveforms with respect to time to avoid power dissipation at the transistor. The ideal class-E PA not only achieves ZVS but it also achieves zero voltage-derivative switching (ZVDS), hence the switching losses are either eliminated or significantly reduced. Because power converters are required to be efficient, high-frequency designs focus mainly around switching or harmonically terminated circuits such as the class-D, class-F, and class-E amplifiers.

#### 2.1.1 HIGH-FREQUENCY SWITCHING LOSSES AND SOFT SWITCHING

There are several ways in which a semiconductor device operating as a switch can incur losses generally attributed to "switching losses." The reverse-recovery process of a diode, dissipated energy stored in the output capacitance of a FET, or losses due to the current tailing typical of thyristors and IGBT are some known examples. Because the majority of the designs presented in this thesis use a High Electron Mobility Transistor (HEMT), which is a form of Field Effect Transistor (FET) [33], only the switching losses most common to FETs are addressed.

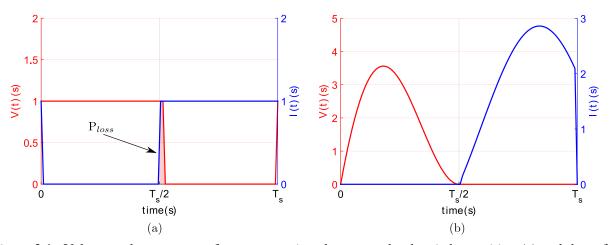

The ON-OFF and OFF-ON transition of switching converters can be classified as hard-switched, zerocurrent switched, or zero-voltage switched. Generally, when a transistor employs ZVS and ZCS during the switching transitions, it is said to use soft switching. Circuits with hard-switched operation such as PWM converters depend on voltage and current waveforms changing abruptly from a high value to zero when the switch is turned ON and OFF. In FETs, and specifically HEMTs, the majority of the switching losses occur due to the energy stored in the output capacitance of the transistor. When the transistor is switched OFF, there is almost no loss, because the output capacitance of the transistor holds the voltage across the transistor at nearly zero volts, and the current that was previously flowing through the switch, starts flowing through the output capacitor. However when the switch is turned ON, the energy stored in a FET output capacitance at the time the switch is turned ON, is completely dissipated in the transistor's ON resistance. Fig. 2.1 shows a simplified comparison between the voltage and current waveforms of a transistor operating under

Figure 2.1: Voltage and current waveforms comparison between a hard-switch transition (a) and the softswitching transition of a class-E amplifier (b). The voltage and current waveforms are normalized to the voltage and current of the supply.

hard-switching and a transistor operating under soft-switching conditions.

The energy stored in the output capacitance of the transistor is given by

$$W = \frac{1}{2}C_{out}V^2 \tag{2.1}$$

and depends only on the output capacitance and the voltage across the transistors. Hence reducing the ON resistance of the transistor has no effect in the switching power lost and since  $C_{out}$  is an inherent parameter of the transistor, the only option left is to ensure the transistor turns ON when there is zero voltage across the switch. This is one of the reasons why ZCS has little to no effect in the switching losses of MOSFETS [27] or why the ZCS class-E PA is not as efficient as the ZVS version [29]. Furthermore, the total switching power loss is given by

$$P_{loss} = \frac{1}{2} f C_{out} V^2 \tag{2.2}$$

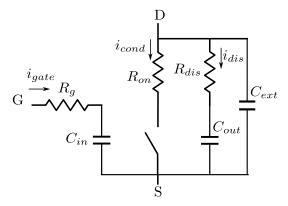

which increases linearly with frequency. Thus, at high-frequencies it is imperative to operate the transistor in ZVS. A simplified model of the parasitic components that cause loss in a MOSFET presented in [34] is shown in Fig. 2.2. The model ignores the coupling drain to gate capacitance  $C_{gd}$ .  $R_{on}$ ,  $R_{dis}$  and  $R_{g}$ correspond to conduction loss, displacement loss, and gating loss, respectively.  $C_{in}$  and  $C_{out}$  are the input and output capacitance, while  $C_{ext}$  is the external capacitance. Conduction loss is proportional to  $R_{on}$  and independent of frequency. However, both  $i_{disp}$  and  $i_{gate}$  are directly proportional to frequency because the impedance of both  $C_{in}$  and  $C_{out}$  decreases linearly with frequency. Furthermore, because gating losses and displacement losses are of the form  $i^2R$ , the losses are proportional to  $f^2$ . Table 2.1 summarizes the losses in hard-switched and soft-switched converters and how they scale with frequency.

Figure 2.2: Simplified model of a MOSFET and the main parasitic components that cause power loss. The simplified model ignores the coupling drain to gate capacitance  $C_{gd}$ .

| Loss                 | Hard-switched           | Soft-switched                |

|----------------------|-------------------------|------------------------------|

| Conduction           | $i_{cond,RMS}^2 R_{on}$ | $i_{cond,RMS}^2 R_{on}$      |

| Gating               | $C_{in}f_{sw}$          | $C_{in}^2 R_{gate} f_{sw}^2$ |

| Off-state conduction | N/A                     | $C_{out}^2 R_{dis} f_{sw}^2$ |

| Overlap              | $f_{sw}$                | N/A                          |

| Cap. discharge       | $C_{out}f_{sw}$         | N/A                          |

Table 2.1: Soft-switched vs. hard-switched loss

There has been extensive research and many topologies have been proposed to achieve soft switching via resonant converters [35, 36] or by modifying PWM converters by implementing resonant switches [37, 38]. More recently, architectures suitable for VHF operation are presented on [39, 40], where an unregulated 100 MHz converter consisting of a class-E inverter with a self-oscillating gate driver and a resonant rectifier achieved 75 % efficiency at 4 W output power. A feedback network provides the required phase shift between the fundamental component of the drain voltage and the gate signal to attain sustain oscillations

and minimize gating losses. Similarly in [41], a class-E inverter with a self-oscillating gate driver and a class-E rectifier using a shunt diode achieved 55 % efficiency with an output power of 1.7 W switching at approximately 100 MHz. In both cases conduction losses due to the ON resistance of the transistor  $R_{on}$  and conduction losses in the resonant inductors contribute to most of the power losses. This highlights one of the main disadvantages of using resonant topologies. Resonant topologies transfer power at the fundamental frequency component, as opposed to PWM converters that transfer power at DC, fundamental frequency, and harmonics. This causes very high current and voltage peaks through resonant networks and switching elements. The high-current spikes cause an increase in conduction losses that can sometimes undermine or even outweigh the reduction in switch losses at high frequencies. Additionally, resonant topologies are optimized for a single load and their performance declines when operating with a big range of loads.

Most of the recent work at VHF has focused on class-E converters or derivatives of it. Class-E PAs and class-E rectifiers offer the advantage of an additional degree of soft switching achieved by enforcing not only ZVS but ZDVS or zero derivate voltage switching. Enforcing ZDVS means that not only is the voltage across the switch zero when the switch turns ON, but the derivative of the voltage across the switch is also 0. A class-E inverter enforces both ZVS and ZDVS only for the optimum design load  $R_{opt}$ . However, a class-E inverter can still operate under ZVS for a load  $0 > R > R_{opt}$  with the use of an anti-parallel or a series diode ensuring low to non-existent switching losses. A detailed analysis of a class-E<sup>2</sup> dc-dc converter is shown in subsection 3.2.1

#### 2.2 MAGNETICS

Magnetic components such as inductors and transformers have been a bottleneck in the development of high frequency and integrated power converters. Not only are magnetics usually the largest component of a converter, making integration difficult or impossible, but magnetic components used at high frequencies fail to achieve comparable electrical performance to their low frequency counterpart. Transformers are seldom used at frequencies above a couple of megahertz because of the increase in losses with frequency, hence this section will focus on inductors used in resonant circuits. Losses in a resonant inductors can be generally

divided into core losses and winding losses. At frequencies used in this thesis (>1 GHz), magnetic and ferrite cores have high loss, and are therefore not considered.

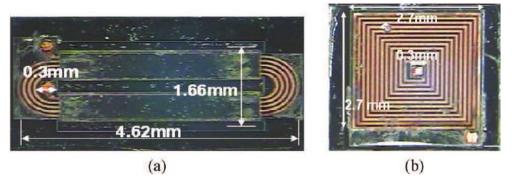

Using low permeability RF materials [42], can extend the performance of cored inductors up to the HF region (3-30 MHz) but not much more. Currently available cored magnetics thus present a fundamental frequency limit and therefore high frequency magnetic component have to rely on coreless or air-core designs. Air-core inductors are inductors without a magnetic core, the actual core of the inductor does not need to be air and can be made out of a dielectric. The majority of the inductors used in UHF and microwave frequencies are built with a core made out of ceramic. Up to date, most if not all the inductors used in power converters operating above 50 MHz are [7] either discrete or on-chip integrated air-core inductors. Even in the development of on-chip integrated inductors, core losses present a limit in operating frequency. A comparison between the performance of an air-core inductor and a magnetic-core inductor on silicon is shown in [1]. The magnetic-core inductor is a racetrack design and the air-core inductor is a square spiral design, both are described in [43]and are shown in Fig. 2.3 It is found that the magnetic-core inductor performs better up to 50 MHz, but the air-core inductor performs similar or better from 70-100 MHz due to high eddy current loss in the core material.

Figure 2.3: Top view of (a) fabricated magnetic-core microinductor and (b) air-core inductor compared in [1]

#### 2.2.1 Winding losses

As shown in the previous section the use of cored inductors is limited to the VHF region, therefore circuits operating at higher frequencies are required to use coreless or air-core inductors. In an air-core inductor

conduction losses produced by the resistance of the conductor are the main source of loss. At DC and lower frequencies, the power loss in the windings can be simply expressed as

$$P_{cu} = I_{RMS}^2 R_{DC} \tag{2.3}$$

however, at high frequencies, eddy-currents induced in the winding conductors can increase winding losses via the skin effect and the proximity effect. The skin effect causes high-frequency currents to congregate at the surface of the conductor without penetrating to the center of the conductor, effectively reducing the cross-sectional area. The skin depth of a conductor is given by

$$\delta = \sqrt{\frac{\rho}{\pi \mu f}} \tag{2.4}$$

where  $\rho$  is the resistivity of the conductor, f is the frequency of the current waveform, and  $\mu$  is the permeability of the conductor which is equal to  $\mu_0$  for most conductors. The penetration depth of a copper conductor is

$$\delta = \frac{7.5}{\sqrt{f}}cm\tag{2.5}$$

Additionally, a conductor carrying a high-frequency current produces a field that can induce more complex eddy-currents in other windings. The proximity effect can sometimes increase the effective ac resistance  $R_{ac}$  more than the skin effect [44]. There are two approaches to mitigating the proximity effect. One is to use conductors that are small compared to the skin depth to avoid giving room for eddy-currents to circulate in a conductor. An example is the use of litz-wire in in wire-wound components [45]. The other approach, is the configuration of the windings in a single layer in such a way that the current can flow on the surface of that layer in a region one skin-depth deep [46].

In the case of air-core inductors, specially inductors used for RF application, the performance of the component is usually quantified by the quality factor Q. Where Q is the ratio between inductive and resistive impedance magnitudes and can be expressed as

$$Q = \frac{\omega L}{R_{ac}} \tag{2.6}$$

Typical Q values of RF inductors are approximately in the 50-100 range. Table 2.2 shows a comparison of some of the 10-nH low profile air-core RF inductors from Coilcraft®. The Q of all of the inductors is less than 100 at approximately 1 GHz. The high-frequency resistance can be obtained from the Q values provided by the manufacturer. For example, all of the discrete inductors used in the designs of the converter presented in Chapter 4 are non-magnetic inductors with a ceramic core from Coilcraft®. According to [47], all of the frequency dependent losses are included in the measurement of Q, including skin effect, proximity effect, and core losses when relevant.

Table 2.2: Typical RF inductors from coilcraft

| Part number   | Inductance | Q             | SRF   | DC resistance | Irms |

|---------------|------------|---------------|-------|---------------|------|

|               | (nH)       |               | (GHz) | $(m\Omega)$   | (mA) |

| 0402HP-10NX-L | 10         | 62 @ 900 MHz  | 4.70  | 110           | 1300 |

| 0603HP-10NX-L | 10         | 90 @ 900 MHz  | 4.30  | 48            | 1400 |

| 0805HT-10NT-L | 10         | 55 @ 750 MHz  | 3.30  | 80            | 800  |

| 0807SQ-10N_L  | 10.2       | 100 @ 400 MHz | 4     | 7             | 2700 |

| 1606-9_L      | 9.85       | 100 @ 800 MHz | 5.2   | 13            | 1600 |

| 1606-9_L      | 9.85       | 100 @ 800 MHz | 5.2   | 13            | 1600 |

#### 2.3 Semiconductor device technology

For high-frequency dc-dc converters to offer comparable performance to readily available low frequency converters, the semi-conductor device used as the switching element is required to have exceptional electrical characteristics. The output capacitance  $C_{out}$ , the input capacitance  $C_{in}$ , and the ON resistance  $R_{ON}$  are of particular importance for high-efficiency. Typical MOS devices used in power converters can efficiently operate into the low VHF region but not much higher than that. [48] shows a comparison of MOS devices operating above 30 MHz. A list of 10 devices the authors identified as good candidates for high-frequency operation under soft-switching, and soft-gate switching is provided. The authors note that a subset of the

devices shown has been used to realize designs operating up to 110 MHz at tens of Volts. Silicon devices are generally limited by low breakdown field, low thermal conductivity (operating at junction temperature around 200° C) and limited switching frequency. Wide band-gap semiconductors such as GaN, SiC, and diamond offer the potential to overcome all of the limitations of silicon technology except current price. Various properties of wide bandgap semiconductors are summarized in Table 2.3 for comparison with silicon [49]. A wider band-gap means the semiconductor device has higher activation energies and can operate at higher voltages and higher temperatures. High-electron mobility is related to high-frequency operation, while high saturation drift velocity is directly proportional to high-frequency switching capabilities [50].

Diamond offers the highest bandgap, highest electric-breakdown field, highest thermal conductivity, and highest saturated E-drift velocity. Nonetheless, research in diamond semi-conductors is at an infant stage and currently diamond has a number of problems related to device fabrication that need to be solved before it becomes a viable technology [49, 50].

| Material | $\mu_n$     | $\mu_p$     | $\epsilon_r$ | Eg      | E <sub>c</sub> | λ            | V <sub>sat</sub>  |

|----------|-------------|-------------|--------------|---------|----------------|--------------|-------------------|

|          | Electron    | Hole        | Dielectric   | Bandgap | Breakdown      | Thermal      | Saturated         |

|          | mobility    | mobility    | constant     |         | field          | Conductivity | E-drift velocity  |

|          | $(cm^2/Vs)$ | $(cm^2/Vs)$ |              | (eV)    | (kV/cm)        | (W/cm-K)     | (cm/s)            |

| Si       | 1450        | 450         | 11.7         | 1.12    | 300            | 1.3          | 107               |

| GaAs     | 8500        | 400         | 12.9         | 1.4     | 400            | 0.54         | $2 \times 10^{7}$ |

| 6H-SiC   | 415         | 90          | 9.7          | 2.9     | 2500           | 5            | $2 \times 10^{7}$ |

| GaN      | 1000        | 350         | 8.9          | 3.39    | 5000           | 1.3          | $2 \times 10^{7}$ |

| Diamond  | 2200        | 1800        | 5.7          | 5.6     | 56000          | 20           | $3 \times 10^{7}$ |

Table 2.3: Table of properties of major wide band-gap materials

GaN devices are the obvious candidate to replace LDMOS and GaAs in RF and microwave applications due to their high frequency performance at a higher voltage. In specific, the GaN HEMT can alleviate many of the problems presented by LDMOS devices, such as low input and output impedances. The material properties of GaN HEMTs, such as breakdown field, mobility, and speed, lend themselves to high-power switching applications with a projected  $V_{BR}^2/R_{ON}$  hundred times larger than in silicon [49].