# Broadband Supply Modulated PAs for Efficient and Linear Transmit Arrays

by

### Connor Nogales

B.S., Northwest Nazarene University, 2019M.S., University of Colorado, Boulder, 2021

A thesis submitted to the

Faculty of the Graduate School of the

University of Colorado in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

2024

Committee Members:

Gregor Lasser, Chair

Zoya Popović

Dragan Maksimović

Taylor Barton

Joshua Hawke

Christian Fager

Nogales, Connor (Ph.D., Electrical Engineering)

Broadband Supply Modulated PAs

for Efficient and Linear Transmit Arrays

Thesis directed by Prof. Gregor Lasser

Next-generation transmitters require large RF bandwidths, high effective isotropic radiated power (EIRP), broadband signals with a time-varying amplitude, and high power amplifier (PA) efficiency. Broadband architectures at the PA, antenna, and beamforming network achieve large RF bandwidths. Implementing PAs with high output power and high-gain antennas can achieve a high EIRP. However, signals with a time-varying envelope statistically operate most of the time at power levels backed-off from the peak. This substantially reduces PA efficiency, particularly for signals with a high peak-to-average power ratio (PAPR). By dynamically changing the drain supply of the PA, the efficiency can be improved, an approach known as supply modulation.

This thesis addresses the efficiency and linearity enhancement of PAs through dynamic discrete supply modulation. The hardware design and characterization of dynamic supply modulators and PAs suitable for an array of many active elements are investigated. The PAs in this thesis are designed to operate across a 6 GHz to 12 GHz bandwidth and amplify signals with an instantaneous bandwidth ranging from 10 MHz to 67.5 MHz. First, an overview of broadband supply modulation is presented. This thesis begins with the design of a 10 W GaN-on-SiC MMIC PA designed for high efficiency with a dynamic drain supply. The trade-offs between continuous and discrete supply modulation are discussed, and the modulated performance of this PA is examined through simulation.

One challenge identified is the PA's gain magnitude and phase dependence on supply voltage, which can degrade the linearity of supply-modulated PAs. Through load/source pull simulation and measurement of a fabricated 5 W GaN-on-SiC MMIC PA, it is shown that by deviating from conventional PA match for efficiency or output power and instead matching for low gain variation,

the PA's supply-modulated performance can be improved.

Additionally, a high-power discrete supply modulator is designed to generate a drain waveform suitable for many PA elements with a shared drain supply. Through careful selection of

the switching transistors, this modulator achieves a peak output power of 800 W and a switching

frequency of  $10 \,\mathrm{MHz}$ . Parasitics in the output trace interconnect and switching devices create significant ringing upon voltage level transition. The ringing is reduced by pulsing the gates of the

transistors briefly before turning them on. This puts the transistors in a lossy state and dampens

the ringing with a small cost to efficiency ( $\sim 1\%$  point).

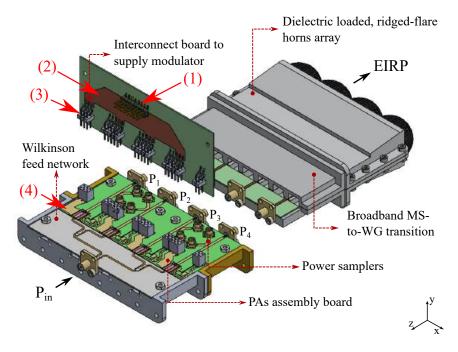

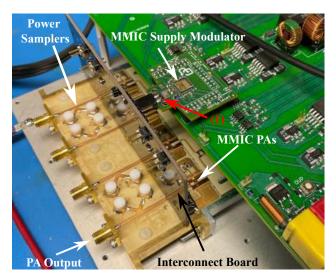

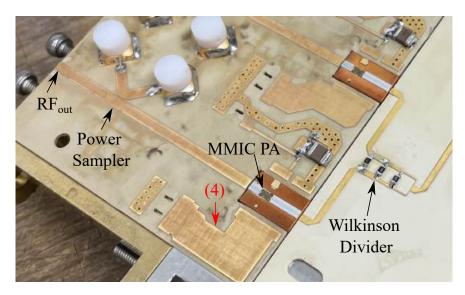

Integrating a dynamic supply modulator with an active array is an additional challenge. For instance, the drain bias interconnect must have low inductance and capacitance to avoid low-pass filtering the dynamic drain signal. Additionally, broadband antennas are not always perfectly matched to  $50\,\Omega$  and, therefore, can degrade the PA performance. These challenges are investigated through the dynamic supply measurements of a  $4\times 1$  antenna array with four commercially available GaN MMIC PAs supplied by an MMIC GaN supply modulator with a switching speed of  $100\,\mathrm{MHz}$ . This thesis concludes with a summary of contributions and an overview of future work.

### Dedication

To my parents and Sierra.

### Acknowledgements

First of all, my advisors, Gregor Lasser, and Zoya Popović, deserve very special thanks for all the long hours they worked with me to get to this point. Thank you, Gregor, for all the time you spent pouring over my designs, data, and papers, along with always being available to meet and guide me through this Ph.D. journey. Without your guidance and support, I certainly would not be where I am today. Thank you, Zoya, for adopting me into your already large group of students, making sure I had funding through my whole Ph.D., helping me with my writing, and keeping the lab full of equipment to do interesting experiments, along with all the other incredible things she does for me and my colleagues.

I would like to thank Dr. Laila Martzal for all the mentorship she has provided me and for letting me use her fantastic design of the antenna array and feed network. Big thanks to Paul Flaten for letting me use his supply modulator MMIC and for helping me with measurements and our chats in the lab. I would like to thank Reyes for putting up with me all these years as we sat next to each other and for keeping things interesting in the lab; it has been a pleasure watching you develop as an RF engineer. You have made this journey much more enjoyable for me.

I would like to thank all of Zoya's current and former group members with whom I have had the pleasure of working over the years. It's been a ride. Big thanks to Devon Donahue for his advice on life and microwaves as well as the rest of the RF Ph.D. students at CU and my professors.

Finally, I would like to thank all my roommates over the years for the adventures we had, my family for their emotional support and encouragement, and my fiancee, Sierra, for her unconditional love and support.

# Contents

# Chapter

| 1 | Intr | oductio | n                                             | 1  |  |

|---|------|---------|-----------------------------------------------|----|--|

|   | 1.1  | Backg   | round and Motivation                          | 1  |  |

|   | 1.2  | Power   | Amplifier Overview                            | 6  |  |

|   |      | 1.2.1   | Class-B PA                                    | 7  |  |

|   |      | 1.2.2   | Communication and Test Signals                | 9  |  |

|   | 1.3  | PA Ef   | ficiency Enhancement Techniques               | 15 |  |

|   |      | 1.3.1   | Doherty PA                                    | 16 |  |

|   |      | 1.3.2   | Outphasing PA                                 | 18 |  |

|   |      | 1.3.3   | Load Modulated Balanced Amplifier             | 19 |  |

|   |      | 1.3.4   | Supply Modulation                             | 19 |  |

|   | 1.4  | Thesis  | S Organization                                | 21 |  |

| 2 | Broa | adband  | Supply Modulated PA System Aspects            | 24 |  |

|   | 2.1  | Introd  | luction                                       | 24 |  |

|   | 2.2  | Broad   | band PA Design and Non-linearities            | 25 |  |

|   |      | 2.2.1   | Waveform Engineering                          | 25 |  |

|   |      | 2.2.2   | Overdriven class-A PA                         | 27 |  |

|   |      | 2.2.3   | Broadband MMIC PA Design and Characterization | 29 |  |

|   | 2.3  | Suppl   | y Modulator Architectures                     | 37 |  |

|   |      |                                                                  | vii        |

|---|------|------------------------------------------------------------------|------------|

|   | 2.4  | Drain Voltage to Input Power Relationship                        | 40         |

|   |      | 2.4.1 Continuous Shaping Function                                | 42         |

|   |      | 2.4.2 Discrete Shaping Function                                  | 46         |

|   | 2.5  | Summary                                                          | 51         |

| 3 | Sour | rce/Load Impedances Study of Discretely Supply Modulated GaN PAs | <b>53</b>  |

|   | 3.1  | Introduction                                                     | 53         |

|   | 3.2  | Simulation Study                                                 | 56         |

|   |      | 3.2.1 Device source and load pull                                | 56         |

|   |      | 3.2.2 Envelope Simulations of a Single Device                    | 60         |

|   | 3.3  | PA Design and Characterization                                   | 65         |

|   |      | 3.3.1 PA design                                                  | 65         |

|   |      | 3.3.2 Small-Signal Simulations and Measurements                  | 67         |

|   |      | 3.3.3 Large-Signal Simulations and Measurements                  | 68         |

|   | 3.4  | Modulated Drain Voltage Measurements and Experimental Validation | 69         |

|   |      | 3.4.1 Discrete Supply Modulated Results                          | 71         |

|   | 3.5  | Summary                                                          | 73         |

| 4 | High | h Power Discrete Supply Modulator Design and Characterization    | <b>7</b> 5 |

|   | 4.1  | Introduction                                                     | 75         |

|   |      | 4.1.1 Survey of Published Supply Modulators                      | 75         |

|   | 4.2  | High Power Transistor Survey and Comparison                      | 78         |

|   | 4.3  | Supply Modulator Design and Simulation                           | 84         |

|   |      | 4.3.1 Reverse Device Operation                                   | 86         |

|   | 4.4  | Transistor and Output Trace Modeling                             | 87         |

|   |      | 4.4.1 Transistor Model Development                               | 90         |

|   | 4.5  | Dynamic Supply Measurements                                      | 94         |

|   |      | 4.5.1 Test Setup                                                 | 94         |

|              |        |                                               | viii |

|--------------|--------|-----------------------------------------------|------|

|              |        | 4.5.2 Measured Performance Results            | 96   |

|              | 4.6    | Summary                                       | 98   |

| 5            | Ring   | ging Reduction Through Gate Pulsing           | 101  |

|              | 5.1    | Introduction                                  | 101  |

|              | 5.2    | Ringing Origins                               | 103  |

|              | 5.3    | Supply Modulator Test Setup                   | 104  |

|              | 5.4    | Ringing Reduction Comparison                  | 106  |

|              |        | 5.4.1 Gate Resistance Study                   | 106  |

|              |        | 5.4.2 Gate Pulsing and Dead-Time Optimization | 107  |

|              | 5.5    | Summary                                       | 111  |

| 0            | Б      |                                               | 110  |

| 6            |        |                                               | 113  |

|              | 6.1    | Introduction                                  | 113  |

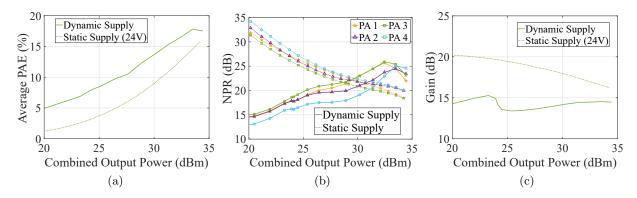

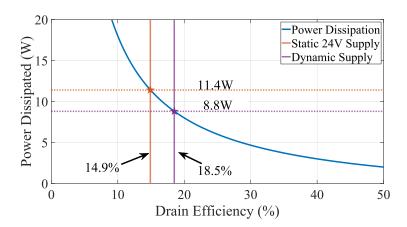

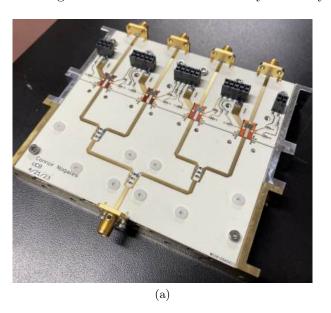

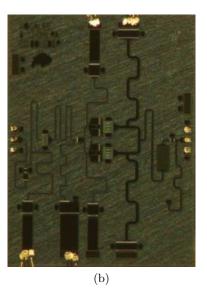

|              | 6.2    | Supply Modulation of a Single Element         | 117  |

|              | 6.3    | Experiment Setup                              | 120  |

|              | 6.4    | Dynamic Supply Measurements of an Array       | 123  |

|              | 6.5    | Summary                                       | 127  |

| 7            | Con    | clusion, Summary, and Future Work             | 129  |

|              | 7.1    | Thesis Conclusion                             | 129  |

|              | 7.2    | Thesis Summary                                | 130  |

|              | 7.3    | Future Work                                   | 135  |

|              |        |                                               |      |

| В            | Biblio | ography 1                                     | 139  |

| A            | ppe    | ndix                                          |      |

| $\mathbf{A}$ | A M    | IMIC PA Designed for High Efficiency          | 151  |

| v |

|---|

|   |

| A.1 | CW Simulation and Measurements        | 151 |

|-----|---------------------------------------|-----|

| A.2 | Modulated Signal Envelope Simulations | 152 |

# Tables

# Table

| 2.1 | Comparison of average PAE, Gain, and EVM for flat-gain, compressed flat-gain,                              |    |

|-----|------------------------------------------------------------------------------------------------------------|----|

|     | and maximum efficiency shaping functions with continuous, discrete, and static $20\mathrm{V}$              |    |

|     | drain supplies at an output power of 33 dBm with the phase variation omitted.                              |    |

|     | There are no bandwidth limitations enforced on the discrete supply                                         | 50 |

| 2.2 | Comparison of average PAE, Gain, and EVM for flat-gain, compressed flat-gain,                              |    |

|     | and maximum efficiency shaping functions with continuous, discrete, and static $20\mathrm{V}$              |    |

|     | drain supplies at an output power of 33 dBm with the phase variation included.                             |    |

|     | There are no bandwidth limitations enforced on the discrete supply                                         | 51 |

| 3.1 | $\Delta  G ,  \Delta \phi,  { m and}   \Delta G$ of the three matching cases                               | 60 |

| 3.2 | Simulated Average PAE, Gain, $P_{\rm out}$ , and EVM for the Three Cases with Static                       |    |

|     | 28 V, Continuous, and Discrete Drain Supplies. The Values are Obtained at a Fixed                          |    |

|     | Output Power of 27 dBm (Left) and a Fixed EVM of 5% (Right)                                                | 64 |

| 4.1 | Key specifications of state-of-the-art continuous and discrete supply modulators with                      |    |

|     | peak output powers up to 500 W in GaN and MOSFET technologies                                              | 78 |

| 4.2 | Key parameters of the Si MOSFET, GaN, and SiC MOSFET transistors with $I_{\rm d-max}$                      |    |

|     | ranging from 10 to 105 A and a minimum $V_{\rm br}$ of 25 V. The associated $R_{\rm on}$ and $C_{\rm out}$ |    |

|     | is plotted vs $I_{\mathrm{d-max}}$ in Fig. 4.2                                                             | 82 |

| 4.3 | Capacitor, packages, and number of elements in each capacitor bank                                         | 84 |

| 4.4 | Intrinsic transistor capacitance as a function of voltage                  |

|-----|----------------------------------------------------------------------------|

| 5.1 | Implemented pulse settings, DT, and NRMSE for the DT optimization and gate |

|     | pulsing techniques with a 5 $\Omega$ load                                  |

| 6.1 | Active impedances presented at each port of the array                      |

# Figures

# Figure

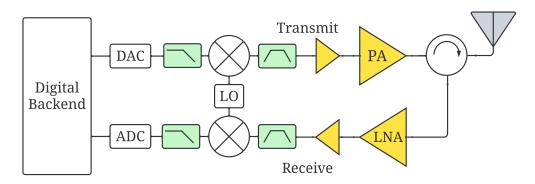

| 1.1 | Generalized Transmit/Receive RF front-end module with a circulator to isolate the              |   |

|-----|------------------------------------------------------------------------------------------------|---|

|     | receive chain from the transmit chain                                                          | 1 |

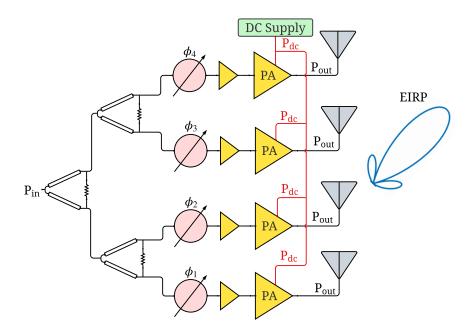

| 1.2 | A 4x1 element active transmit array. The input signal is split four ways through               |   |

|     | symmetric Wilkinson dividers. The phase of each path is controlled with multiple               |   |

|     | phase shifters. Drivers are used to overcome losses in the beamforming network and             |   |

|     | saturate the PA elements                                                                       | 2 |

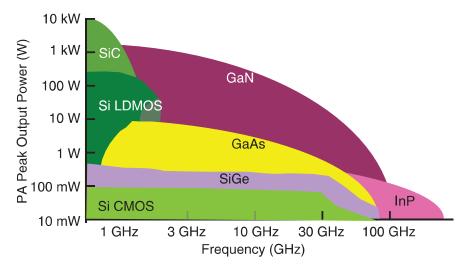

| 1.3 | An overview of semiconductor device power handling vs. frequency. Figure adapted               |   |

|     | from [1, Figure 1, pg. 101]                                                                    | 2 |

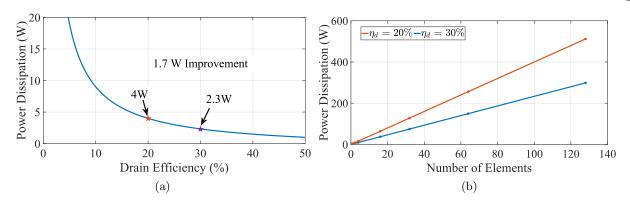

| 1.4 | (a) Power dissipation vs. drain efficiency $(\eta_{\rm d})$ for 1 W of output power. (b) Power |   |

|     | dissipation vs. number of PA elements in a transmit array with a drain efficiency of           |   |

|     | $20\%$ and $30\%$ . The output power of each element is $1\mathrm{W}.$                         | 5 |

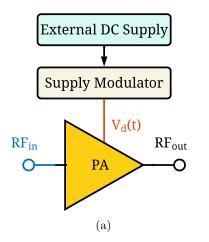

| 1.5 | (a) Simplified block diagram of a supply modulated PA. (b) Time domain input and               |   |

|     | output signal envelope of a GaN on SiC MMIC PA amplyfing a 64-QAM $67.5\mathrm{MHz}$           |   |

|     | signal with dynamic drain voltage                                                              | 6 |

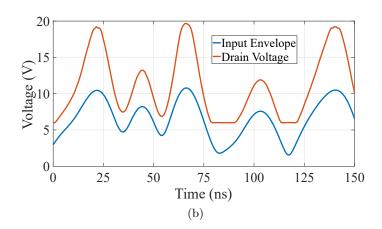

| 1.6 | (a) basic PA schematic, (b) IV curves of a GaN transistor with load lines in class-A,          |   |

|     | B, AB, and C operation with $V_{\rm k}=5{\rm V.}$                                              | 8 |

| 1.7 | Instantaneous (a) drain and (b) input/output voltage and current waveforms for an              |   |

|     | ideal class-B PA at 1 GHz with a dc drain bias of 28 V and $I_{\rm max}$ of 1.43 A             | 9 |

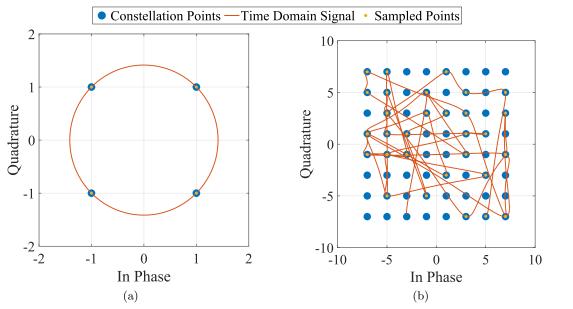

| Comparison of (a) QPSK and (b) 64-QAM constellations. The constellation points                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| are shown in blue. A small section of the baseband signal is shown in orange. Note                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| that the magnitude of the baseband signal is constant for the QPSK signal and                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| changes dynamically with the 64-QAM signal. The symbols in this segment of the                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| signal are shown in yellow, and the time between each symbol is 20 ns, corresponding                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| to a symbol rate of 50 MHz                                                                                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

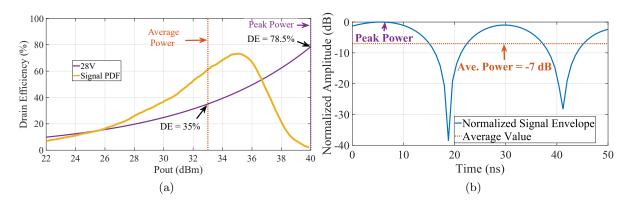

| (a) Ideal class-B PA drain efficiency plotted vs. output power with a 64-QAM signal                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PDF. (b) normalized 64-QAM signal envelope                                                                          | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

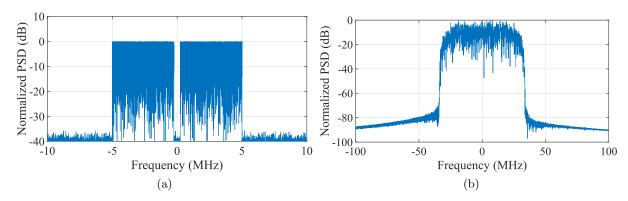

| (a) 10 MHz NPR signals spectrum (b) 67.5 MHz 64-QAM signal with a baud rate of                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 50 Mega-symbols/s and roll-off factor of 0.35                                                                       | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

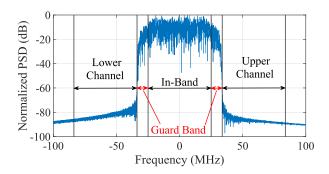

| $67.5\mathrm{MHz}$ $64\mathrm{-QAM}$ signal with a baud rate of $50\mathrm{Mega}$ -symbols/s and roll-off factor of |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $0.35.$ The channel bandwidths are $50\mathrm{MHz}$ wide, and the guard bands are $8.75\mathrm{MHz}$                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| wide                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

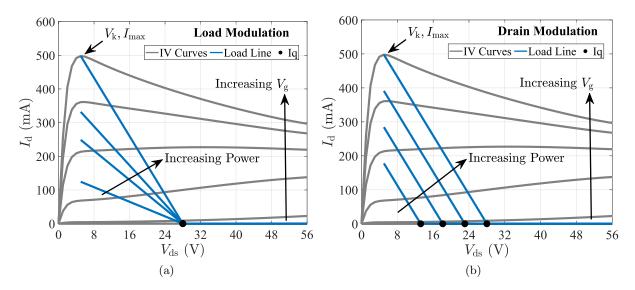

| Example IV curves and load lines of a class-B PA with (a) load modulation and (b)                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| drain supply modulation                                                                                             | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

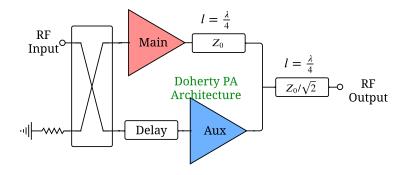

| Block diagram of a Doherty PA                                                                                       | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

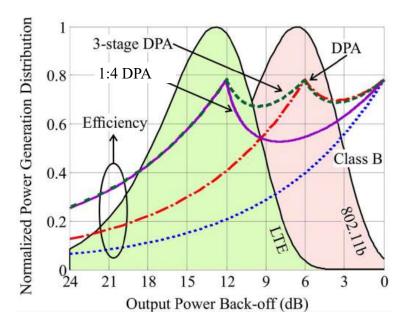

| Efficiency of two-stage, three-stage, and 4-way Doherty PAs with the PDF of LTE                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| and 802.11b signals vs. output power. Figure adapted from [2, Figure 3, pg. 561]                                    | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

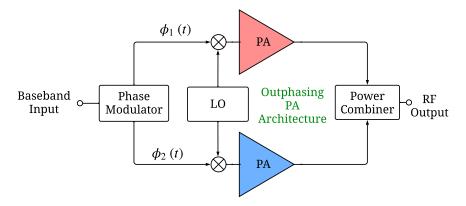

| Block diagram of an outphasing PA. Here the power combiner can be isolated (LINC)                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| or non-isolated (Chireix)                                                                                           | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

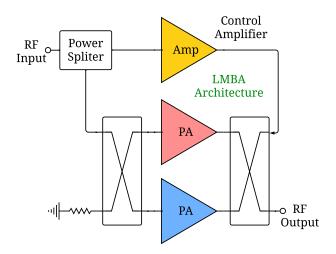

| Block diagram of a LMBA                                                                                             | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

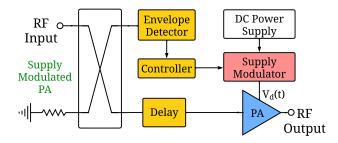

| Block diagram of a supply modulated PA                                                                              | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

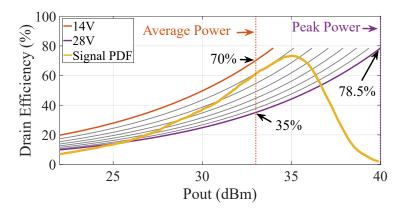

| Drain efficiency $(\eta_d)$ of a class-B PA at multiple drain voltages with the PDF of the                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                     | are shown in blue. A small section of the baseband signal is shown in orange. Note that the magnitude of the baseband signal is constant for the QPSK signal and changes dynamically with the 64-QAM signal. The symbols in this segment of the signal are shown in yellow, and the time between each symbol is 20 ns, corresponding to a symbol rate of 50 MHz.  (a) Ideal class-B PA drain efficiency plotted vs. output power with a 64-QAM signal PDF. (b) normalized 64-QAM signal envelope.  (a) 10 MHz NPR signals spectrum (b) 67.5 MHz 64-QAM signal with a baud rate of 50 Mega-symbols/s and roll-off factor of 0.35.  67.5 MHz 64-QAM signal with a baud rate of 50 Mega-symbols/s and roll-off factor of 0.35. The channel bandwidths are 50 MHz wide, and the guard bands are 8.75 MHz wide.  Example IV curves and load lines of a class-B PA with (a) load modulation and (b) drain supply modulation.  Block diagram of a Doherty PA  Efficiency of two-stage, three-stage, and 4-way Doherty PAs with the PDF of LTE and 802.11b signals vs. output power. Figure adapted from [2, Figure 3, pg. 561] .  Block diagram of an outphasing PA. Here the power combiner can be isolated (LINC) or non-isolated (Chireix).  Block diagram of a LMBA . |

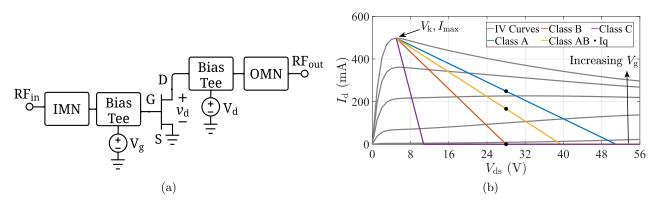

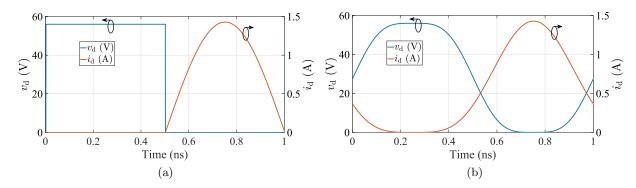

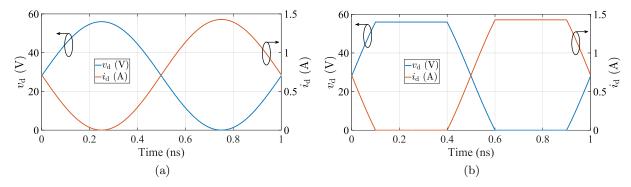

| 2.1  | Drain voltage and current waveforms of a class-F PA with (a) an infinite number                             |    |

|------|-------------------------------------------------------------------------------------------------------------|----|

|      | of harmonics optimally terminated and (b) up to the third harmonic terminated for                           |    |

|      | maximally flat waveforms. For this example the dc drain voltage is 28 V and the                             |    |

|      | transistor maximum current is 1.43 A                                                                        | 26 |

| 2.2  | Overdriven ideal class-A PA drain waveforms operating at 1 GHz. (a) Waveforms                               |    |

|      | when the PA is driven to its maximum without clipping. (b) Waveforms when the                               |    |

|      | PA is driven 3 dB into compression                                                                          | 27 |

| 2.3  | PAE and gain of an overdriven class-A PA plotted vs. output power                                           | 28 |

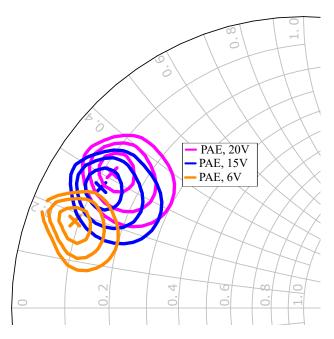

| 2.4  | Load pull of $20 \times 100 \mu\mathrm{m}$ device at drain voltages of 6, 15, and 20 V and 9 GHz each       |    |

|      | with a maximum PAE of $69.8\%$ , $70.0\%$ , and $69.3\%$ , respectively. The contours are                   |    |

|      | in 5% steps referenced to the maximum PAE at the center of each contour                                     | 30 |

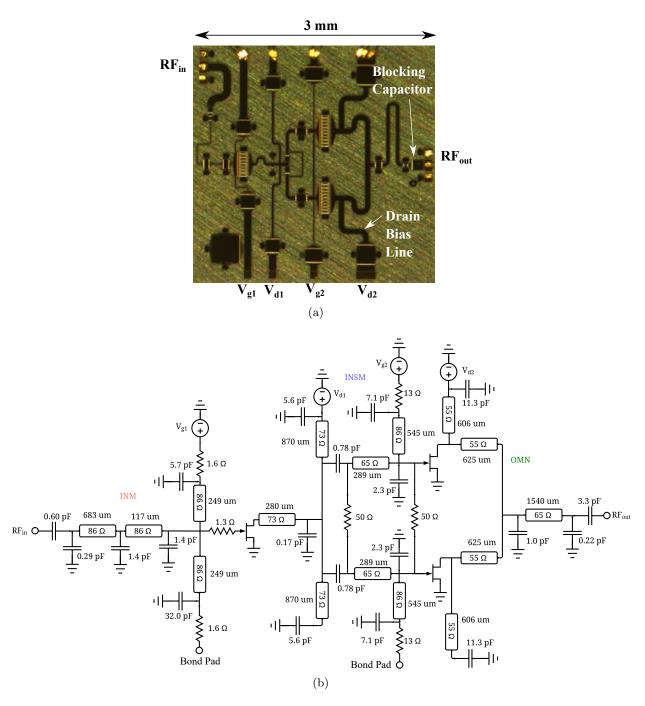

| 2.5  | (a) Photograph of the $10\mathrm{W}$ MMIC operating from $6\mathrm{GHz}$ to $12\mathrm{GHz}.$ (b) Schematic |    |

|      | of MMIC matching network and bias tee                                                                       | 32 |

| 2.6  | Sweep of the $2^{\rm nd}$ harmonic phase when the $3^{\rm rd}$ harmonic is fixed with an open and           |    |

|      | short at an $f_0$ of 6 GHz                                                                                  | 33 |

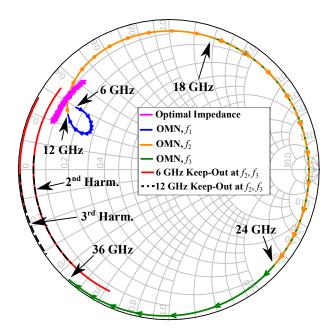

| 2.7  | Efficiency-optimal fundamental load-pull impedance for the final stage device at 15 V,                      |    |

|      | compared to the implemented fundamental, $2^{\rm nd}$ , and $3^{\rm rd}$ harmonic impedances and            |    |

|      | corresponding keep out regions at the band edges as defined in Fig. 2.6                                     | 34 |

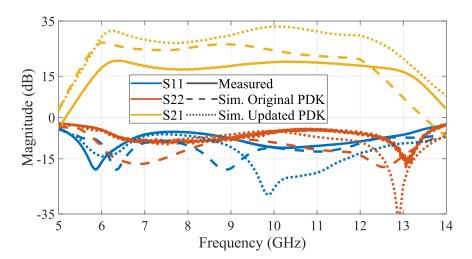

| 2.8  | Measured magnitude of scattering parameters of the PA compared to simulated                                 |    |

|      | results using two different PDKs at a drain voltage of 20 V                                                 | 34 |

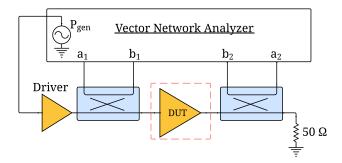

| 2.9  | Large-signal vector measurement setup using external dual-directional couplers to                           |    |

|      | measure the "a" and "b" waves of the PA                                                                     | 35 |

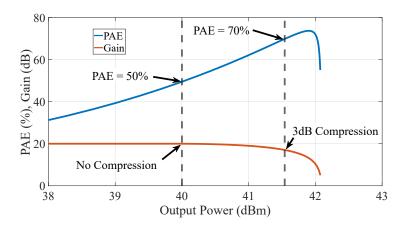

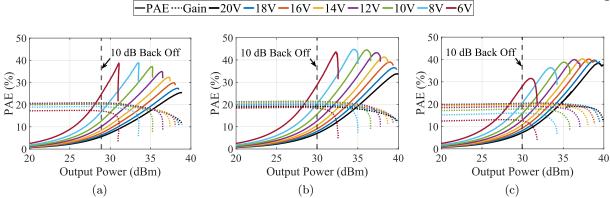

| 2.10 | Measured PAE and gain vs. output power for drain voltages ranging from $6\mathrm{V}$ to                     |    |

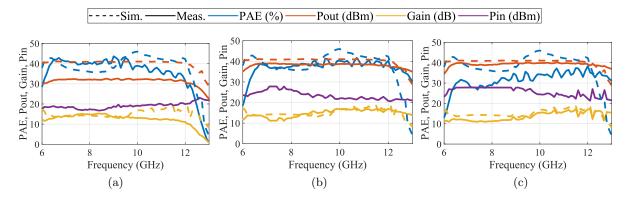

|      | $20\mathrm{V}$ at frequencies of (a) 6.3 GHz, (b) 9 GHz, (c) 12 GHz                                         | 36 |

| 2.11 | PAE, output power, and gain with the drive power at each frequency optimized for                            |    |

|      | PAE at drain voltages of (a) 6 V, (b) 15 V, and (c) 20 V                                                    | 36 |

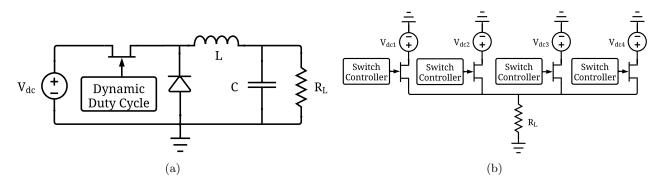

| 2.12 | Power converter schematic for (a) buck converter (b) multi-level converter                                  | 38 |

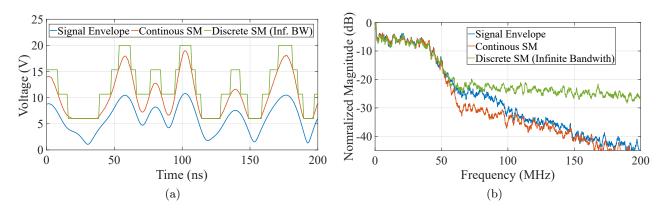

| 2.13 | Example of continuous and discrete drain waveforms along with a 64-QAM $67.5\mathrm{MHz}$              |    |

|------|--------------------------------------------------------------------------------------------------------|----|

|      | signal envelope in the (a) time domain and (b) frequency domain. There are no                          |    |

|      | bandwidth limitations imposed on the discrete waveform                                                 | 39 |

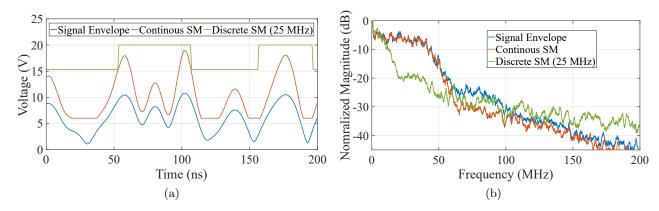

| 2.14 | Example of continuous and discrete drain waveforms along with a 64-QAM $67.5\mathrm{MHz}$              |    |

|      | signal envelope in the (a) time domain and (b) frequency domain. The maximum                           |    |

|      | switching frequency of the discrete waveform is limited to $25\mathrm{MHz.}$                           | 39 |

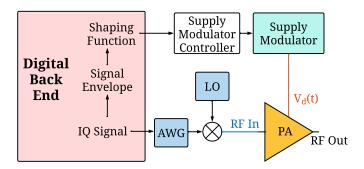

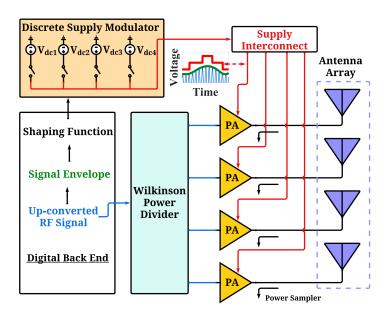

| 2.15 | Block Diagram of a supply modulated PA. The digital back-end programs the arbi-                        |    |

|      | trary waveform generator and supply modulator controller to create the IQ signal                       |    |

|      | and drain voltage. The shaping function LUT is implemented digitally and used to                       |    |

|      | relate the input envelope to the desired drain voltage waveform                                        | 41 |

| 2.16 | Continuous supply modulation trajectories of the MMIC PA at $6.5\mathrm{GHz}$ with the                 |    |

|      | following shaping functions: (a) flat-gain, (b) compressed flat-gain, and (c) maximum                  |    |

|      | efficiency                                                                                             | 43 |

| 2.17 | Continuous supply modulation trajectories of the MMIC PA at $11.5\mathrm{GHz}$ with the                |    |

|      | following shaping functions: (a) flat-gain, (b) compressed flat-gain, and (c) maximum                  |    |

|      | efficiency                                                                                             | 43 |

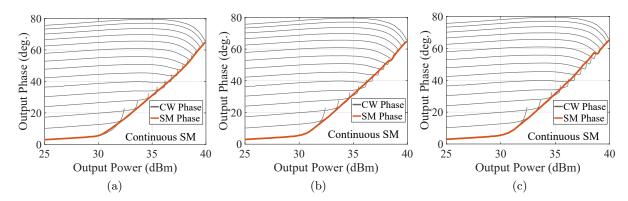

| 2.18 | Continuous supply modulation phase of the $10\mathrm{W}$ MMIC PA at $6.5\mathrm{GHz}$ with the         |    |

|      | following shaping functions: (a) flat-gain, (b) compressed flat-gain, and (c) maximum                  |    |

|      | efficiency                                                                                             | 44 |

| 2.19 | Continuous supply modulation phase of the $10\mathrm{W}$ MMIC PA at $11.5\mathrm{GHz}$ with the        |    |

|      | following shaping functions: (a) flat-gain, (b) compressed flat-gain, and (c) maximum                  |    |

|      | efficiency                                                                                             | 44 |

| 2.20 | Continuous shaping function at frequencies of (a) $6.5\mathrm{GHz}$ and (b) $11.5\mathrm{GHz}$ . Three |    |

|      | shaping functions are used at each frequency. The first is flat-gain, the second is                    |    |

|      | compressed flat-gain with $1\mathrm{dB}$ of compression, and the third is maximum efficiency.          | 45 |

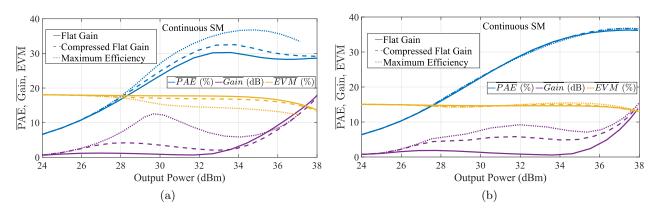

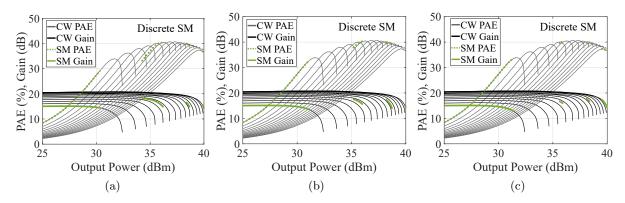

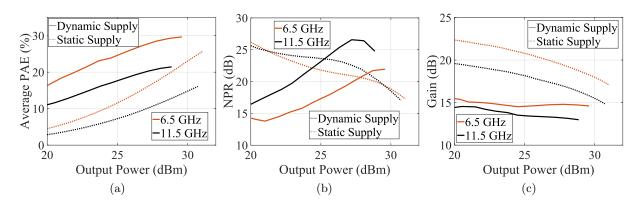

| 2.21 | Predicted PAE, EVM, and Gain of the MMIC PA with a continuous dynamic supply                         |    |

|------|------------------------------------------------------------------------------------------------------|----|

|      | amplifying a 64-QAM 67.5 MHz signal at (a) 6.5 GHz and (b) 11.5 GHz. Flat-gain,                      |    |

|      | compressed flat-gain, and maximum efficiency shaping functions are used, and the                     |    |

|      | trajectories are shown in Fig. 2.16 and Fig. 2.17. These results omit the phase                      |    |

|      | variation of the PA                                                                                  | 45 |

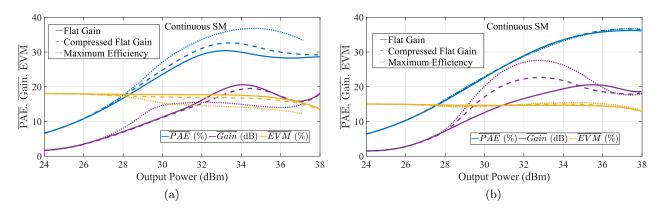

| 2.22 | Predicted PAE, EVM, and Gain of the MMIC PA with a continuous dynamic supply                         |    |

|      | amplifying a 64-QAM 67.5 MHz signal at (a) 6.5 GHz and (b) 11.5 GHz. Flat-gain,                      |    |

|      | compressed flat-gain, and maximum efficiency shaping functions are used, and the                     |    |

|      | trajectories are shown in Fig. 2.16 and Fig. 2.17. These results <b>include</b> the phase            |    |

|      | variation of the PA                                                                                  | 46 |

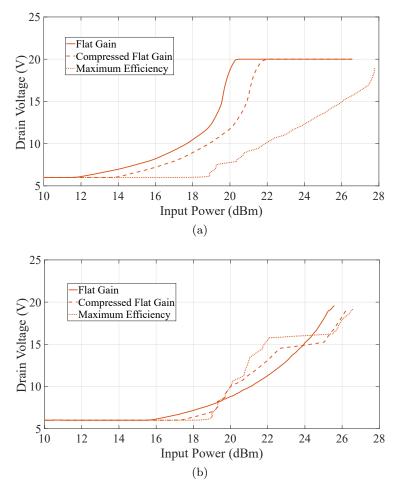

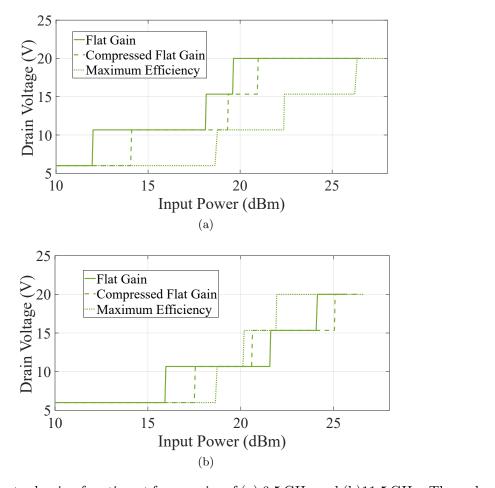

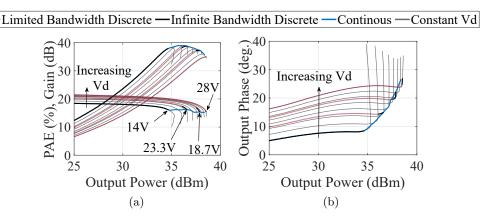

| 2.23 | Discrete shaping function at frequencies of (a) $6.5\mathrm{GHz}$ and (b) $11.5\mathrm{GHz}$ . Three |    |

|      | shaping functions are used at each frequency. The first is flat-gain, the second is                  |    |

|      | compressed flat-gain with $1\mathrm{dB}$ of compression, and the third is maximum efficiency.        | 47 |

| 2.24 | Discrete supply modulation trajectories of the MMIC PA at $6.5\mathrm{GHz}$ with the following       |    |

|      | lowing shaping functions: (a) flat-gain, (b) compressed flat-gain, and (c) maximum                   |    |

|      | efficiency                                                                                           | 48 |

| 2.25 | Discrete supply modulation trajectories of the MMIC PA at $11.5\mathrm{GHz}$ with the following      |    |

|      | lowing shaping functions: (a) flat-gain, (b) compressed flat-gain, and (c) maximum                   |    |

|      | efficiency                                                                                           | 48 |

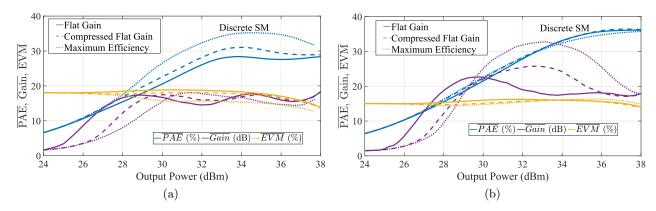

| 2.26 | Predicted PAE, EVM, and Gain of the MMIC PA with a discrete dynamic supply                           |    |

|      | amplifying a 64-QAM 67.5 MHz signal at (a) 6.5 GHz and (b) 11.5 GHz. Flat-gain,                      |    |

|      | compressed flat-gain, and maximum efficiency shaping functions are used, and the                     |    |

|      | trajectories are shown in Fig. 2.24 and Fig. 2.25                                                    | 49 |

| 2.27 | Predicted PAE, EVM, and Gain of the MMIC PA with a discrete dynamic supply                           |    |

|      | amplifying a 64-QAM 67.5 MHz signal at (a) 6.5 GHz and (b) 11.5 GHz. Flat-gain,                      |    |

|      | compressed flat-gain, and maximum efficiency shaping functions are used, and the                     |    |

|      | trajectories are shown in Fig. 2.24 and Fig. 2.25                                                    | 50 |

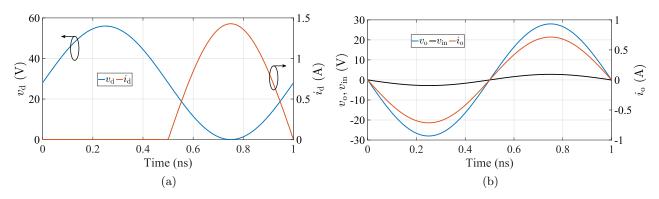

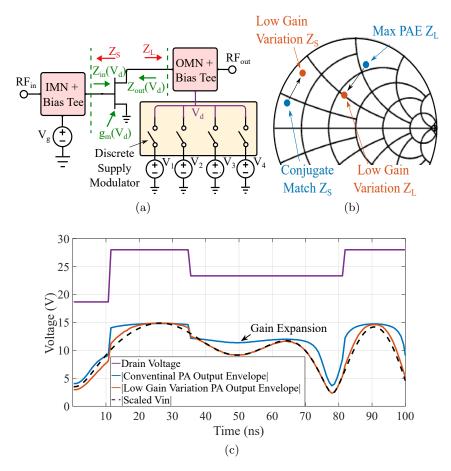

| 3.1 | (a) Block diagram of a PA with a dynamically changing discrete drain supply voltage.                  |    |

|-----|-------------------------------------------------------------------------------------------------------|----|

|     | (b) Potential source/load impedances for low gain variation across drain voltage and                  |    |

|     | conventional PA design impedances. (c) Time domain simulation comparing the                           |    |

|     | conventional PA design to the deliberately mismatched PA designed to reduce the                       |    |

|     | gain dependence on drain voltage.                                                                     | 54 |

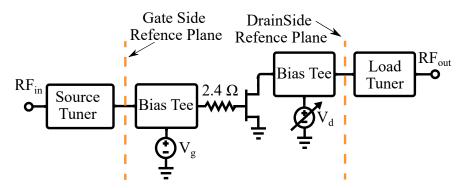

| 3.2 | Source/load pull schematic. The $2.4\Omega$ resistor is added to stabilize the transistor             | 56 |

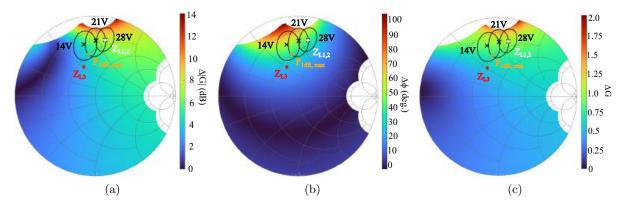

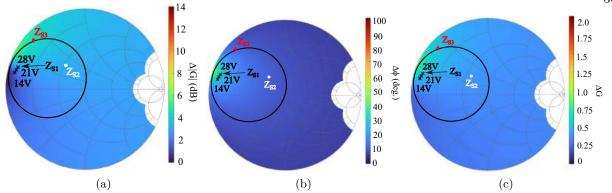

| 3.3 | Load pull at 9 GHz of a single $8\times100\mu\mathrm{m}$ device in the WIN NP15 GaN on SiC            |    |

|     | 150 nm process showing small signal (a) gain magnitude variation $(\Delta  G )$ , (b) gain            |    |

|     | phase variation $(\Delta \phi)$ , and (c) normalized complex gain variation $(\Delta G)$ across drain |    |

|     | voltages of 14, 21, and 28 V. The PAE contours indicate impedances where the                          |    |

|     | PAE is reduced by $5\%$ from the peak PAE at each drain voltage. Additionally, the                    |    |

|     | impedance which results in the maximum 1 dB compression output power is labeled.                      | 57 |

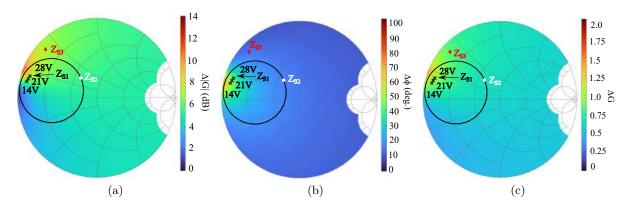

| 3.4 | Source pull at 9 GHz of a single $8{\times}100\mu\mathrm{m}$ device in the WIN NP15 GaN on SiC        |    |

|     | 150 nm process showing small signal (a) gain magnitude variation $(\Delta  G )$ , (b) gain            |    |

|     | phase variation $(\Delta \phi)$ , and (c) normalized complex gain variation $(\Delta G)$ across drain |    |

|     | voltages of 14, 21, and 28 V. The load impedance is fixed at the maximum PAE                          |    |

|     | point for a drain voltage of 28 V $(Z_{L1,2})$ . The conjugate match points at each drain             |    |

|     | voltage are labeled along with the 10 dB small signal gain contour at 14 V                            | 57 |

| 3.5 | Source pull at 9 GHz of a single $8{\times}100\mu\mathrm{m}$ device in the WIN NP15 GaN on SiC        |    |

|     | 150 nm process showing small signal (a) gain magnitude variation ( $\Delta  G $ ), (b) gain           |    |

|     | phase variation $(\Delta \phi)$ , and (c) normalized complex gain variation $(\Delta G)$ across drain |    |

|     | voltages of 14, 21, and $28\mathrm{V}$ . The load impedance is fixed at the mismatched load           |    |

|     | impedance $(Z_{L3})$ . The conjugate match points at each drain voltage are labeled                   |    |

|     | along with the 10 dB small signal gain contour at 14 V                                                | 58 |

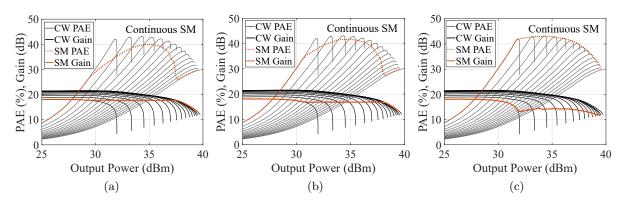

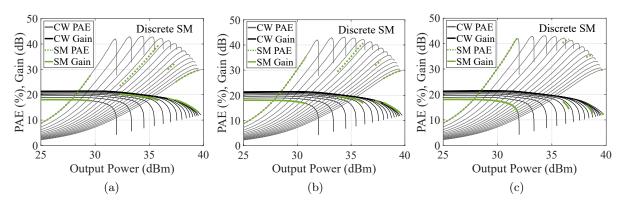

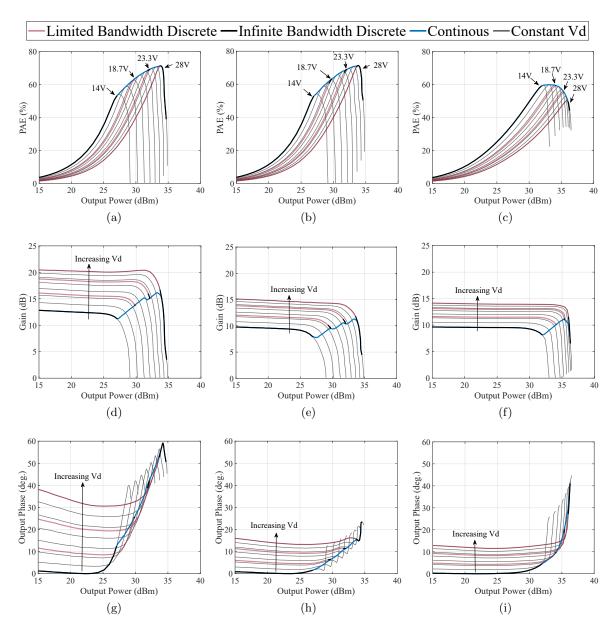

| 3.6  | CW PAE, gain magnitude and phase plotted vs. output power for three different                         |    |

|------|-------------------------------------------------------------------------------------------------------|----|

|      | loading conditions at 9 GHz. The loading conditions are (a) conventional PA design                    |    |

|      | (Case 1), (b) mismatched input impedance for minimal $\Delta\phi$ (Case 2), and (c) PA                |    |

|      | designed for low gain variation with the source and load mismatched (Case 3). Ad-                     |    |

|      | ditionally, the PAE, gain magnitude, and phase resulting from the max PAE shaping                     |    |

|      | function is plotted with an infinite bandwidth supply utilizing continuous (blue) and                 |    |

|      | discrete (black) voltage levels. The performance resulting from bandwidth limita-                     |    |

|      | tions in the discrete supply (red) is shown where the PA operates in the small and                    |    |

|      | large signal regions                                                                                  | 61 |

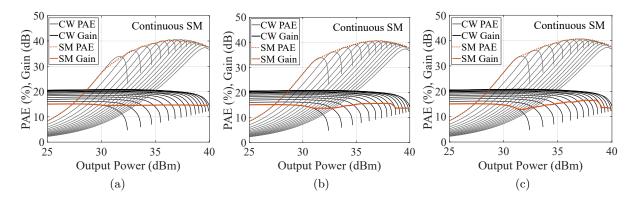

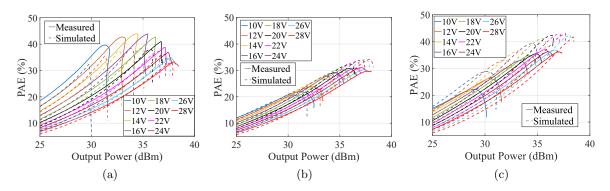

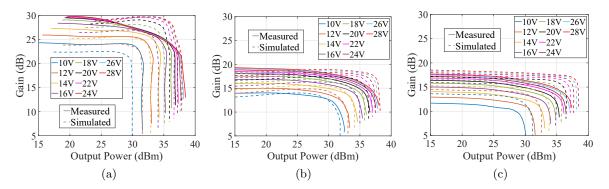

| 3.7  | Simulated comparison between the three loading conditions in terms of average PAE,                    |    |

|      | Gain, and EVM vs output power at 9 GHz with (a) continuous supply modulation                          |    |

|      | (b) four-level discrete supply modulator with a maximum switching frequency of                        |    |

|      | $100\mathrm{MHz}$ and (c) discrete supply modulation with a maximum switching frequency               |    |

|      | of 25 MHz                                                                                             | 62 |

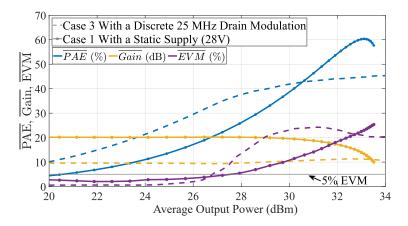

| 3.8  | Simulated comparison between a conventional PA design (Case 1) with a static drain                    |    |

|      | supply and a low gain variation PA design (Case 3) with a discretely supply modu-                     |    |

|      | lated supply at a carrier frequency of $9\mathrm{GHz}$ . The dynamic supply has a maximum             |    |

|      | switching of 25 MHz                                                                                   | 65 |

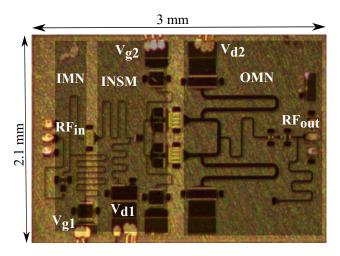

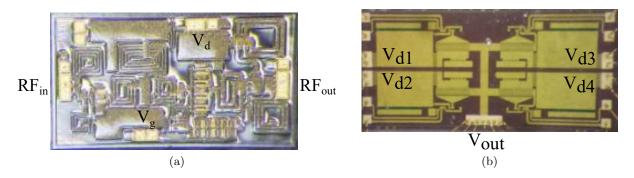

| 3.9  | Photograph of 6 to 12 GHz MMIC PA fabricated in the WIN Semiconductor GaN                             |    |

|      | on SiC NP15 150 nm process                                                                            | 66 |

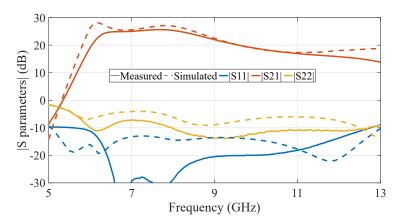

| 3.10 | Measured and simulated S-parameters of the fabricated low gain variation PA at a                      |    |

|      | drain voltage of 28 V                                                                                 | 67 |

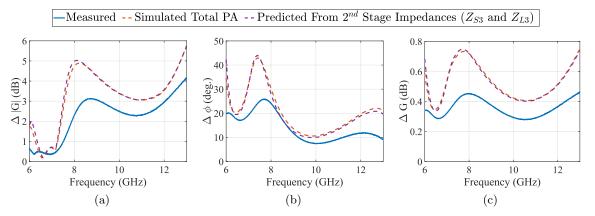

| 3.11 | Measured and simulated small signal (a) gain magnitude variation $(\Delta  G )$ , (b) gain            |    |

|      | phase variation $(\Delta \phi)$ , and (c) normalized complex gain variation $(\Delta G)$ vs frequency |    |

|      | over a 14 to $28\mathrm{V}$ range. The predicted gain variation is calculated by implementing         |    |

|      | the input/output impedance as ideal tuners and cascading them with S-parameters                       |    |

|      | of the final stage transistor at multiple drain voltages as described in section 3.2.1.               | 68 |

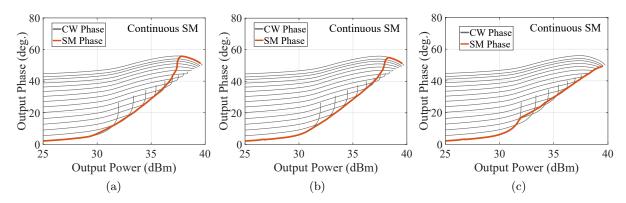

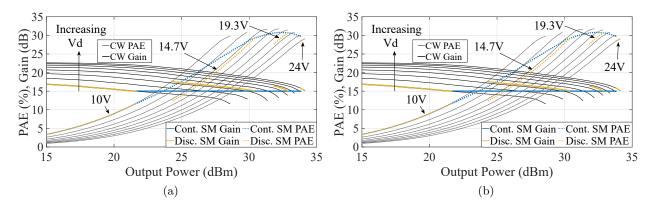

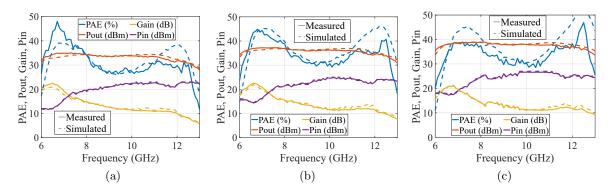

| 3.12 | Measured CW PAE, gain, and phase plotted vs output power at 9 GHz and drain                          |    |

|------|------------------------------------------------------------------------------------------------------|----|

|      | voltages ranging from 14 to 28 V in 2 V steps                                                        | 69 |

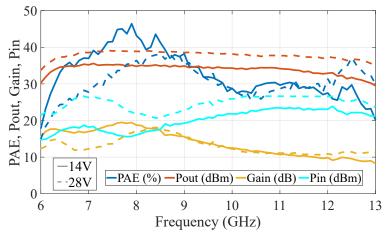

| 3.13 | PAE, gain, output power, and input power vs frequency at drain voltages of 14 and                    |    |

|      | 28 V. Here the input power is selected to yield the highest PAE at each frequency                    |    |

|      | point                                                                                                | 69 |

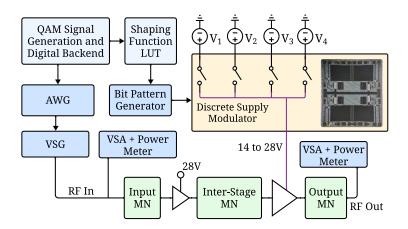

| 3.14 | System block diagram of the measurement system                                                       | 70 |

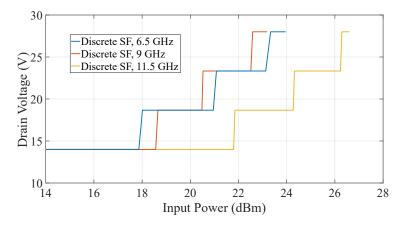

| 3.15 | Discrete shaping functions of the PA at 6.5, 9, and 11.5 GHz                                         | 70 |

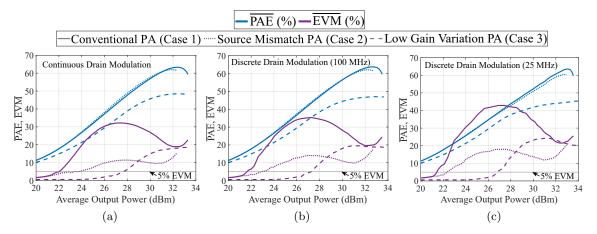

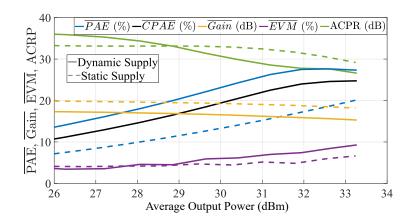

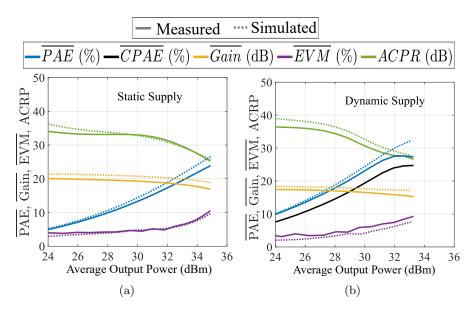

| 3.16 | Measured PA performance with a static 28 V supply and a dynamically changing                         |    |

|      | supply at 9 GHz is shown in (a)                                                                      | 72 |

| 3.17 | Comparison of predicted and measured PA efficiency and linearity at 9 GHz with (a)                   |    |

|      | static $28\mathrm{V}$ supply and (b) dynamically changing four-level supply with a maximum           |    |

|      | switching frequency of 100 MHz.                                                                      | 72 |

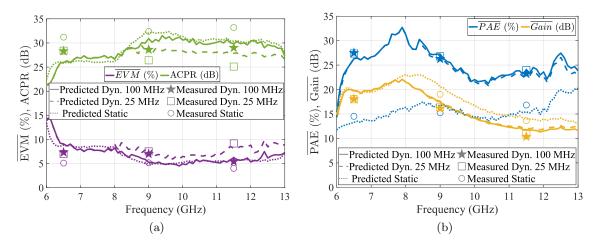

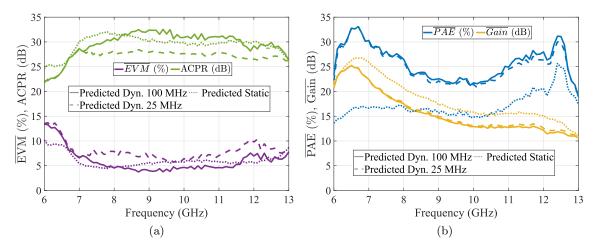

| 3.18 | Measured and predicted results comparing a static 28 V supply to a dynamically                       |    |

|      | changing drain supply with two maximum switching frequencies of $100\mathrm{MHz}$ and                |    |

|      | 25 MHz in terms of (a) linearity and (b) PAE and gain, for a constant output power                   |    |

|      | of 31 dBm. The measured points are plotted at frequencies of 6.5, 9, and 11.5 GHz for                |    |

|      | the static (circle symbols) and dynamic $100\mathrm{MHz}$ (star symbol) and $25\mathrm{MHz}$ (square |    |

|      | symbol) drain voltage cases                                                                          | 73 |

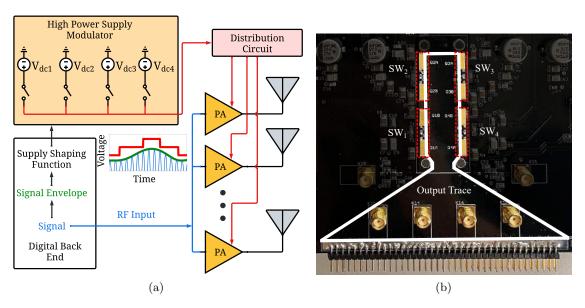

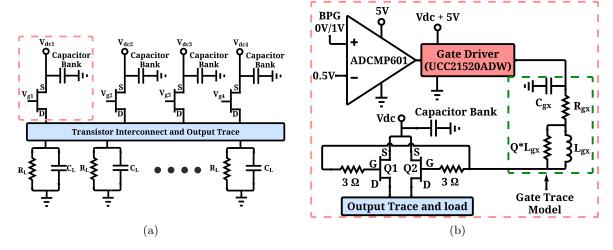

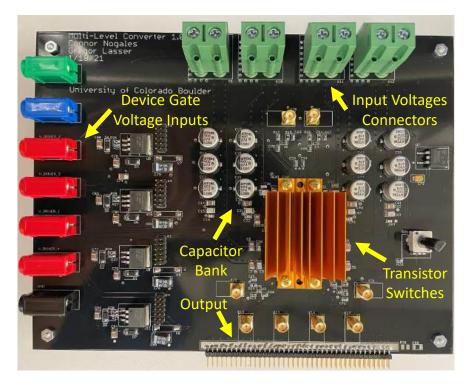

| 1 1  | (a) Plack diagram of a high nerver gunnly modulator simultaneously feeding gaveral                   |    |

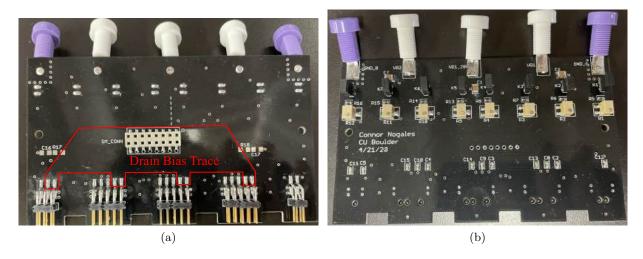

| 4.1  | (a) Block diagram of a high power supply modulator simultaneously feeding several                    |    |

|      | power amplifiers in parallel. The signal envelope (shown in green) is digitally pro-                 |    |

|      | cessed through a shaping function which determines the switch timing and output                      |    |

|      | waveform of the supply modulator. (b) Photograph of the four-level discrete supply                   |    |

|      | modulator with the output trace highlighted and transistor switches labeled. Each                    |    |

|      | switch consists of two transistors in parallel                                                       | 76 |

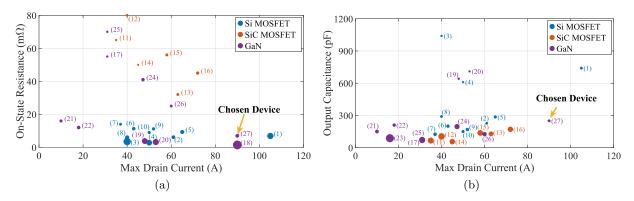

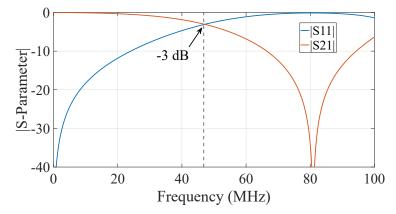

| 4.2 | (a) On-state resistance vs maximum drain current and (b) output capacitance vs                                   |    |

|-----|------------------------------------------------------------------------------------------------------------------|----|

|     | maximum drain current for commercially available transistors in MOSFET, SiC                                      |    |

|     | MOSFET, and GaN technologies. The size of each point in (a) is proportional                                      |    |

|     | to the device $C_{\text{out}}$ and in (b) $R_{\text{on}}$ . Numbers refer to TABLE 4.2                           | 79 |

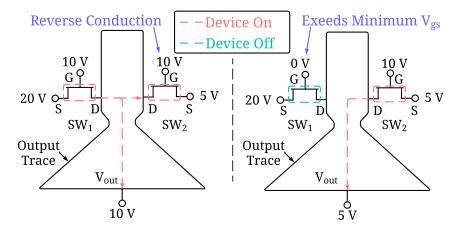

| 4.3 | Cartoon of a two-level supply modulator switching between 20 V (left) and 5 V (right)                            |    |

|     | voltage levels with $V_{\rm gs,min}$ equal to 10 V. The modulator fails since $\Delta V_{\rm out}$ exceeds       |    |

|     | $V_{ m gs,min}$ and violates Eq. 4.1                                                                             | 81 |

| 4.4 | Cartoon of a two-level supply modulator switching between $20\mathrm{V}$ (left) and $10\mathrm{V}$               |    |

|     | (right) voltage levels with $V_{\rm gs,min}$ equal to 10 V. The modulator operates normally                      |    |

|     | since $\Delta V_{ m out}$ is limited to $V_{ m gs,min}$                                                          | 81 |

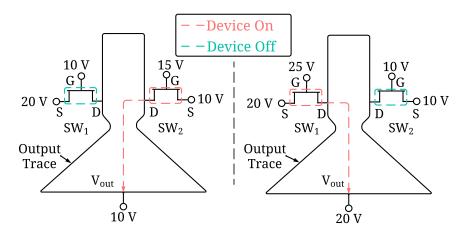

| 4.5 | (a) Overview schematic of the high power multi-level converter. Each parallel RC                                 |    |

|     | circuit represents an individual PA being supply-modulated. (b) Schematic of single                              |    |

|     | switching cell highlighted in the top left of Fig.4.5a. The gate trace is modeled as                             |    |

|     | an RLC circuit with the values extracted from an EM simulation of the trace. $$                                  | 83 |

| 4.6 | Photograph of the high power multi-level converter                                                               | 85 |

| 4.7 | Simulated time domain waveforms of the output and switch 1 gate voltages for                                     |    |

|     | standard and reverse transistor orientations when transitioning from the switch $2$ to                           |    |

|     | switch 4 with an RC load of (1.25 $\Omega$    160 pF). Each respective switch voltage is                         |    |

|     | $V_{ m dc1} = 20V, \ V_{ m dc2} = 16.7V, \ V_{ m dc3} = 13.3V, \ V_{ m dc4} = 10V$ with the gate turn-on voltage |    |

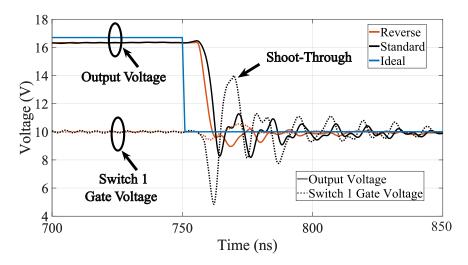

|     | of each switch set to be 5 V above the switch dc voltage                                                         | 86 |

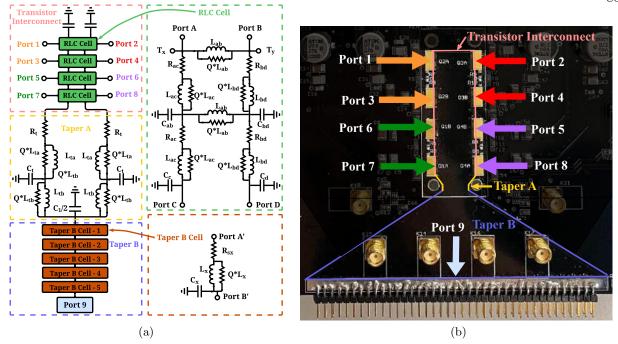

| 4.8 | (a) Schematic of RLC output trace model and (b) associated physical location of the                              |    |

|     | ports in the output trace. The trace is split into three parts: the transistor inter-                            |    |

|     | connect highlighted in pink, taper A highlighted in yellow, and taper B highlighted                              |    |

|     | in purple                                                                                                        | 88 |

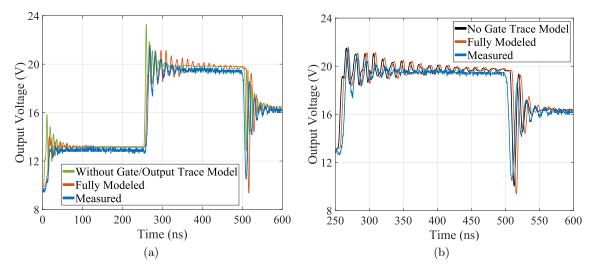

| 4.9 | (a) Simulated HPMLC (a) output voltage, and (b) gate voltage comparing measure-                                  |    |

|     | ment and simulation using different modeling detail on the interconnects using an                                |    |

|     | RC load of $(1.25\Omega \mid\mid 160\mathrm{pF})$                                                                | 89 |

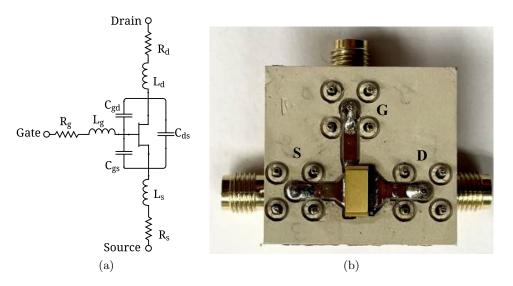

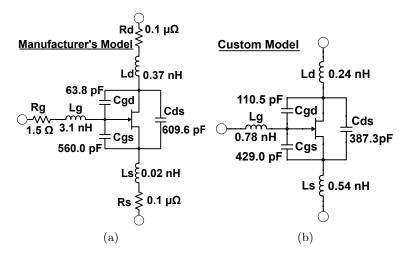

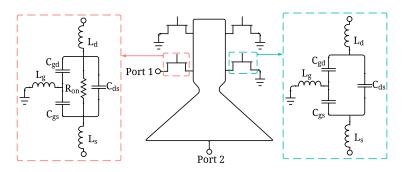

| 4.10 | (a) Schematic of transistor parasitics. (b) Photograph of measurement board milled                    |     |

|------|-------------------------------------------------------------------------------------------------------|-----|

|      | in FR-4 used to measure transistor S-parameters for model reactance extraction. $$ . $$ .             | 91  |

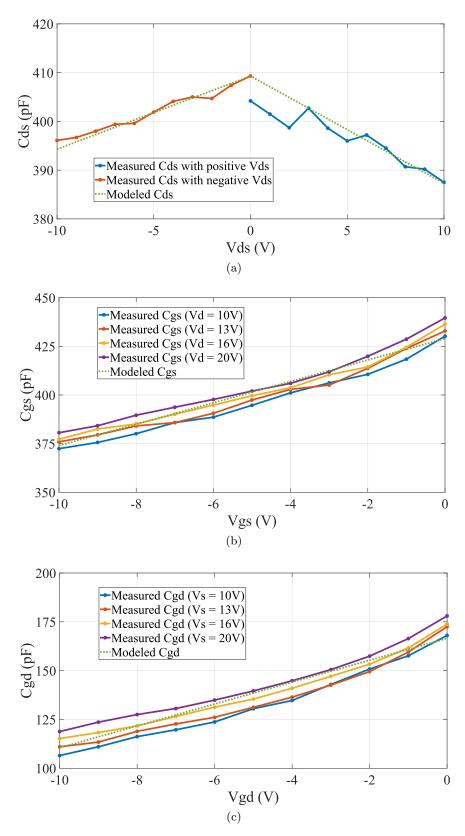

| 4.11 | (a) Measured drain-source capacitance. (b) Measured gate-source and (c) gate-drain                    |     |

|      | capacitance. The dotted green line represents the modeled voltage dependence of                       |     |

|      | each respective capacitance implemented in the new LTspice model                                      | 92  |

| 4.12 | Schematic of transistor parasitic elements with $Vds = 10V$ and $Vgs = 0V$ ex-                        |     |

|      | tracted from (a) manufacturer's LTspice model (b) custom model extracted from                         |     |

|      | S-parameter measurements                                                                              | 93  |

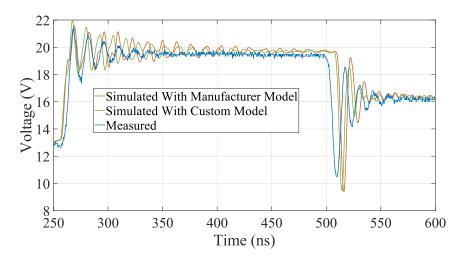

| 4.13 | Output voltage waveform of supply modulator for an RC load (1.25 $\Omega$    160 pF)                  |     |

|      | comparing simulations with manufacturer and custom transistor models against mea-                     |     |

|      | surements                                                                                             | 94  |

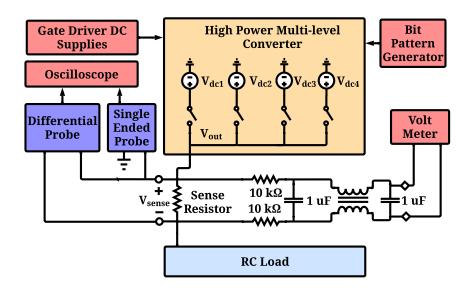

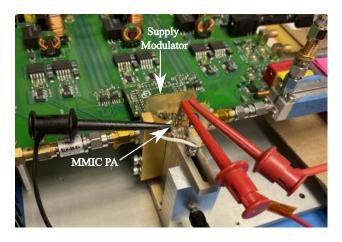

| 4.14 | Test setup block diagram. The current is measured using a differential probe across                   |     |

|      | the sense resistors. The filtered dc component of the voltage drop is used to calibrate               |     |

|      | the offset of the differential probe.                                                                 | 95  |

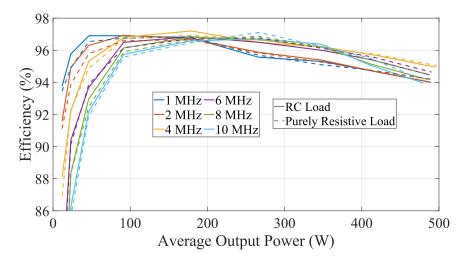

| 4.15 | Supply modulator efficiency with an equal duty cycle four-level waveform at switch-                   |     |

|      | ing frequencies and average output powers ranging from 1 to $10\mathrm{MHz}$ and $11.7\mathrm{W}$ to  |     |

|      | 497.1 W under purely resistive and RC loads                                                           | 97  |

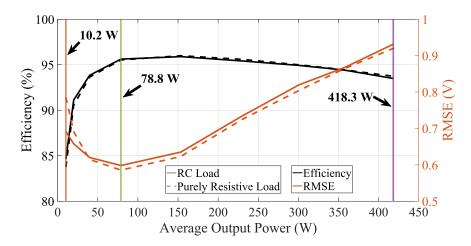

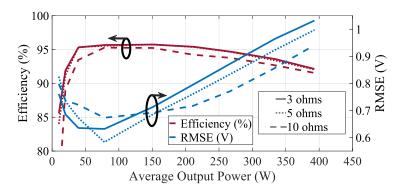

| 4.16 | Supply modulator efficiency and RMSE while tracking an $6.25\mathrm{MHz}$ $64\text{-QAM}$ signal      |     |

|      | between average output powers of $10.2\mathrm{W}$ and $418.3\mathrm{W}$ for a purely resistive and RC |     |

|      | load                                                                                                  | 98  |

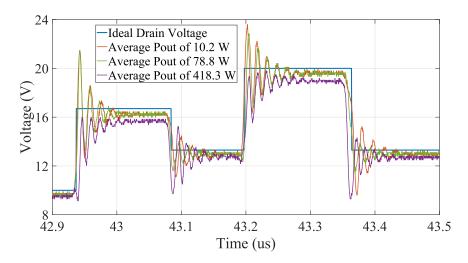

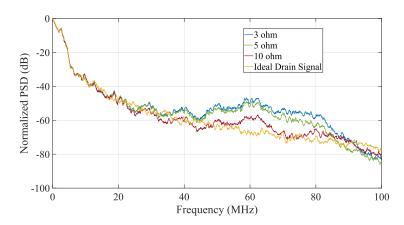

| 4.17 | Measured output voltage with three different parallel RC loads of (20 $\Omega$    10 pF -             |     |

|      | orange), (5 $\Omega$    40 pF - green), and (0.4 $\Omega$    480 pF - purple). These waveforms are    |     |

|      | compared to the ideal drain signal when tracking a 6.25 MHz 64-QAM signal                             | 99  |

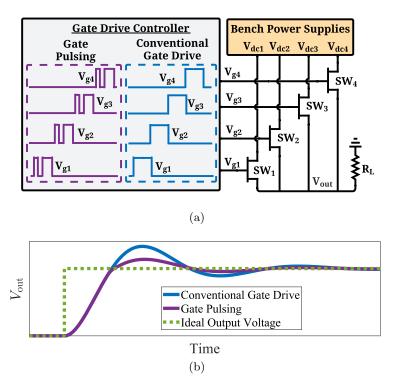

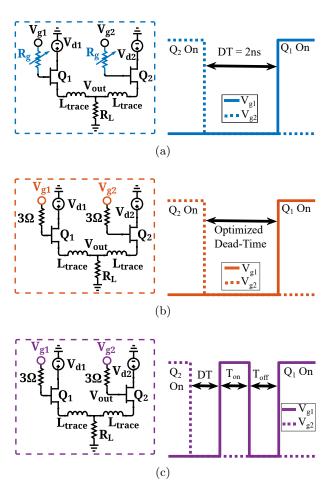

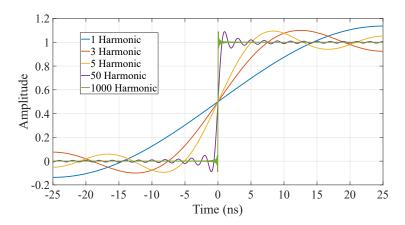

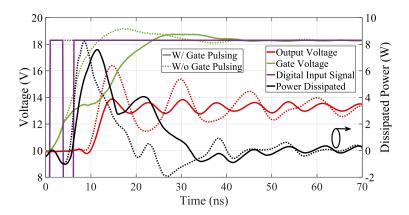

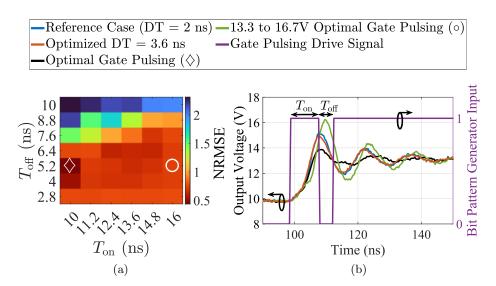

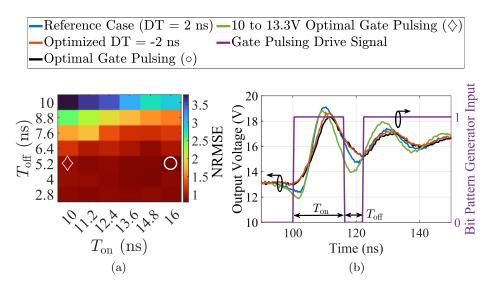

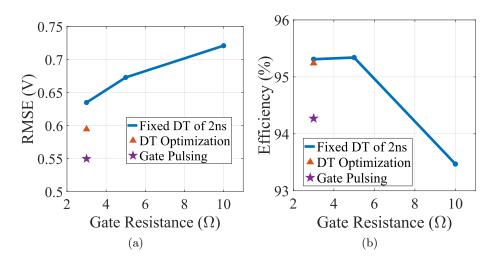

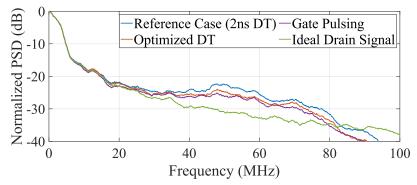

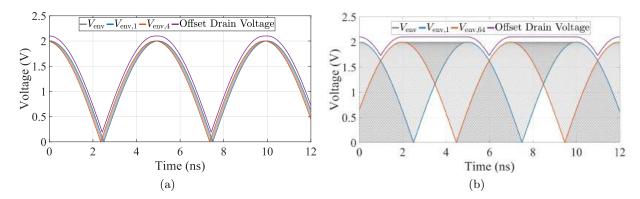

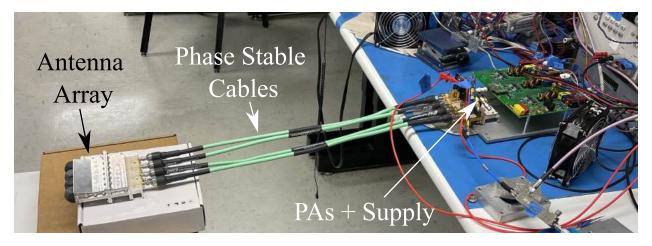

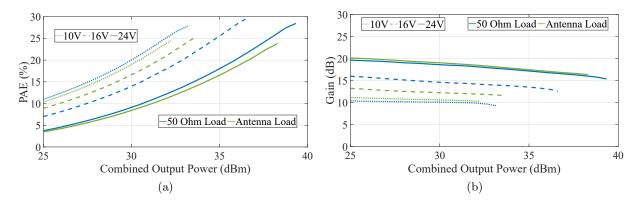

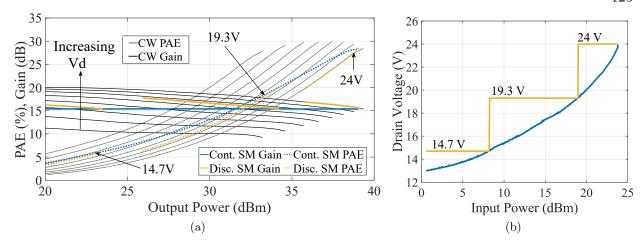

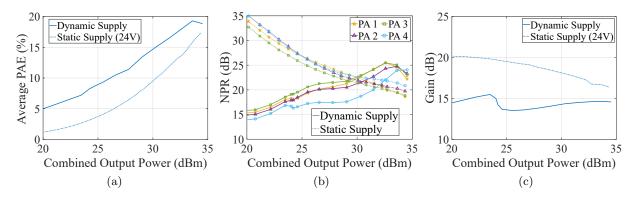

| 5.1  | (a) Schematic and gate drive signals of the high power multi-level converter (b) Ex-                  |     |